# SH960MD-CM236/QM170/HM170

COM Express Basic Module User's Manual

# Copyright

This publication contains information that is protected by copyright. No part of it may be reproduced in any form or by any means or used to make any transformation/adaptation without the prior written permission from the copyright holders.

This publication is provided for informational purposes only. The manufacturer makes no representations or warranties with respect to the contents or use of this manual and specifically disclaims any express or implied warranties of merchantability or fitness for any particular purpose. The user will assume the entire risk of the use or the results of the use of this document. Further, the manufacturer reserves the right to revise this publication and make changes to its contents at any time, without obligation to notify any person or entity of such revisions or changes.

Changes after the publication's first release will be based on the product's revision. The website will always provide the most updated information.

© 2019. All Rights Reserved.

### **Trademarks**

Product names or trademarks appearing in this manual are for identification purpose only and are the properties of the respective owners.

### FCC and DOC Statement on Class B

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- · Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and the receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio TV technician for help.

### **Notice:**

- 1. The changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

- 2. Shielded interface cables must be used in order to comply with the emission limits.

# **Table of Contents**

| Copyright                                                                         | 2      |

|-----------------------------------------------------------------------------------|--------|

| Trademarks                                                                        | 2      |

| FCC and DOC Statement on Class B                                                  | 2      |

| Notice:                                                                           | 2      |

| About this Manual                                                                 | 4      |

| Warranty                                                                          | 4      |

| Static Electricity Precautions                                                    | 4      |

| Safety Measures                                                                   | 4      |

| About the Package                                                                 | 5      |

| Optional Items                                                                    | 5      |

| Before Using the System Board                                                     | 5      |

| Chapter 1 - Introduction                                                          |        |

| Specifications                                                                    |        |

| Features                                                                          |        |

| Chapter 2 - Hardware Installation                                                 |        |

| Board Layout                                                                      |        |

| Standby Power LED                                                                 | 8      |

| System Memory                                                                     | 9<br>q |

| I/O Connectors                                                                    | 11     |

| CPU Fan                                                                           | 11     |

| Board-to-board Connector                                                          |        |

| Signal Descriptions                                                               |        |

| Pin Types                                                                         | 15     |

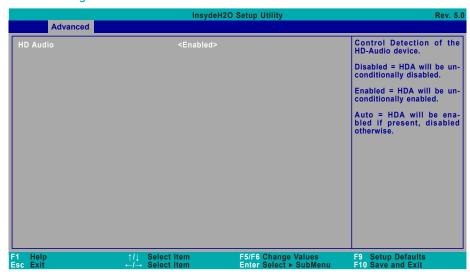

| HDA Śignals Descriptions                                                          | 15     |

| SATA Signals Descriptions                                                         | 16     |

| PCI Express Lanes Signals Descriptions                                            | 17     |

| PEG Signals Descriptions                                                          | 18     |

| ExpressCard Signals Descriptions                                                  | 19     |

| USB Signals Descriptions                                                          |        |

| LPC Signals Descriptions                                                          | ∠1     |

| SPI Signals Descriptions                                                          | 22     |

| VGA Signals Descriptions                                                          | 22     |

| DDI Signals Descriptions                                                          | 23     |

| Serial Interface Signals Descriptions                                             | 25     |

| I2C Signal Descriptions                                                           | 25     |

| Miscellaneous Signal DescriptionsPower and System Management Signals Descriptions | ∠0     |

| Thermal Protection Signals Descriptions                                           | 27     |

| SMBUS Signals Descriptions                                                        | 27     |

| GPIO Signals Descriptions                                                         | 27     |

| Power and GND Signal Descriptions           | 28<br>28 |

|---------------------------------------------|----------|

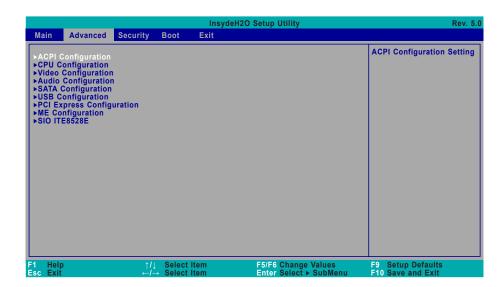

| Chapter 3 - BIOS Setup                      | 29       |

| Overview<br>Main                            |          |

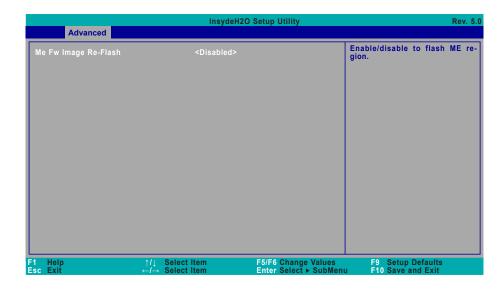

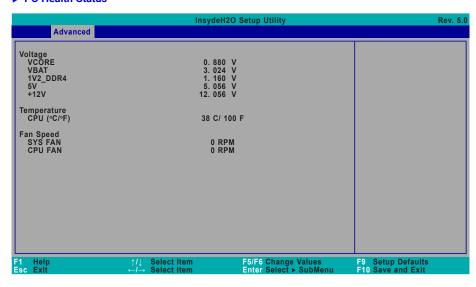

| Advanced                                    |          |

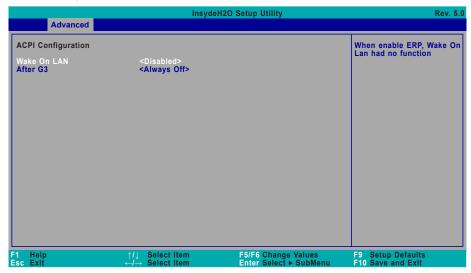

| ACPI Configuration                          | 31       |

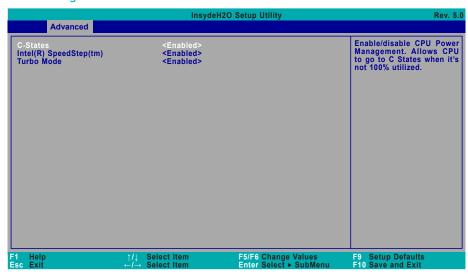

| CPU Configuration                           | 31       |

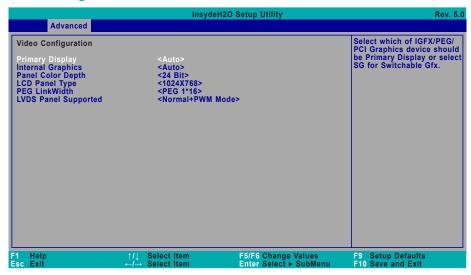

| Video Configuration                         | 32       |

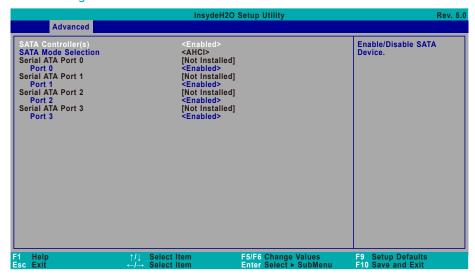

| SATA Configuration                          | 33       |

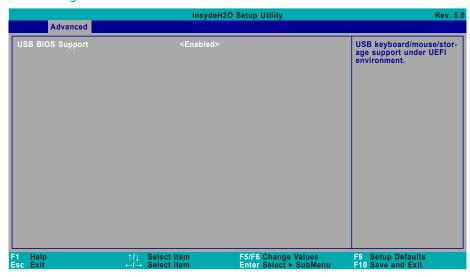

| USB Configuration                           |          |

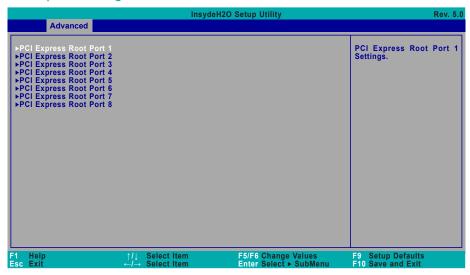

| PCI Express Configuration                   |          |

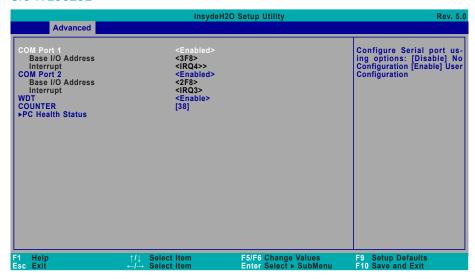

| SIO ITE8528E                                |          |

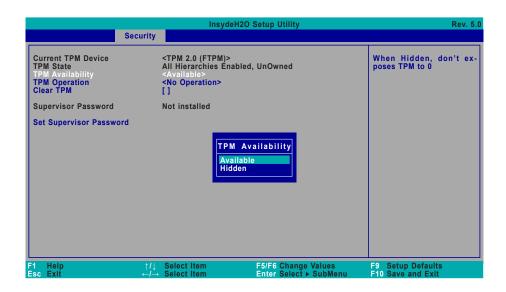

| Security                                    | 36       |

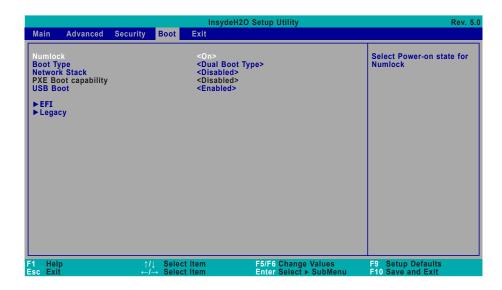

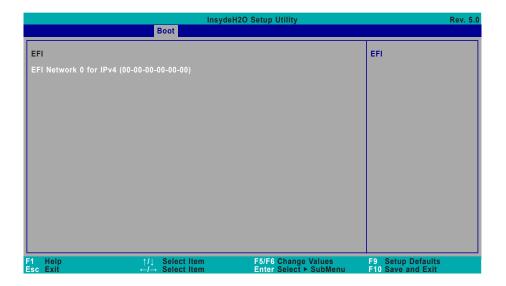

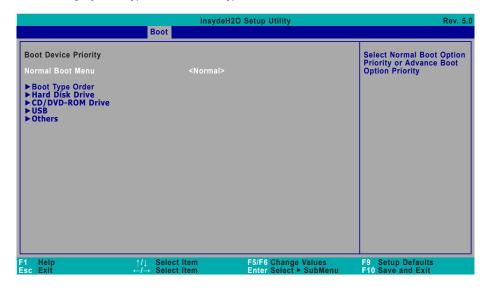

| Boot                                        |          |

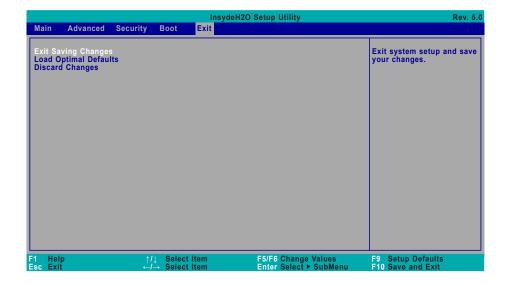

| ExitUpdating the BIOS                       | 38       |

| Notice: BIOS SPI ROM                        | 38       |

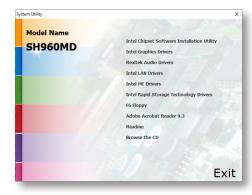

| Chapter 4 - Supported Software              | 39       |

| Auto-run Menu                               |          |

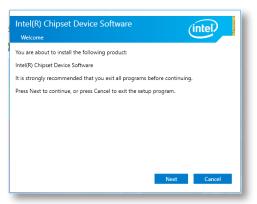

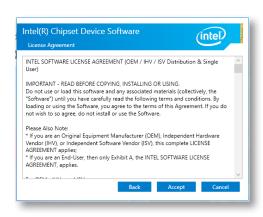

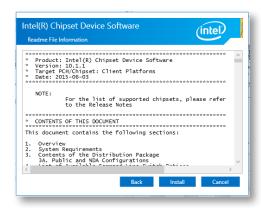

| Intel Chipset Software Installation Utility | 39       |

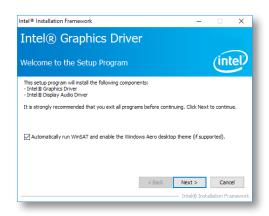

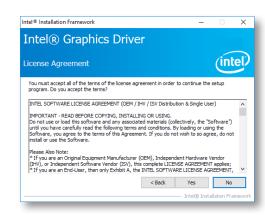

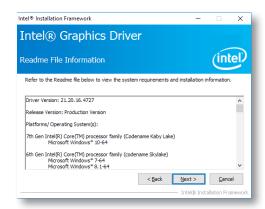

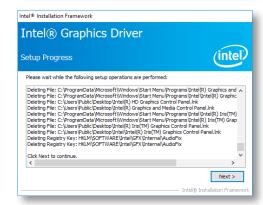

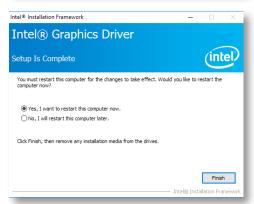

| Intel HD Graphics Drivers                   |          |

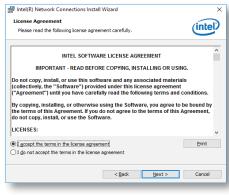

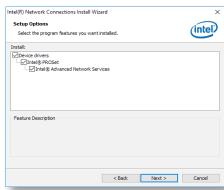

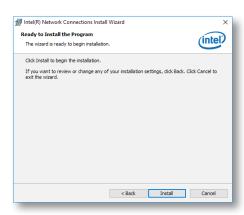

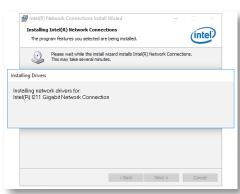

| Realtek Audio DriversIntel LAN Driver       |          |

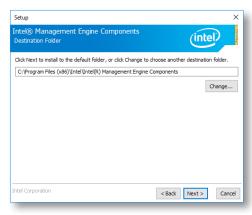

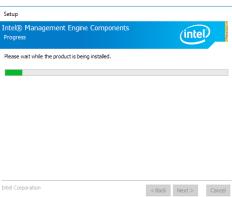

| Intel ME Drivers                            | 43       |

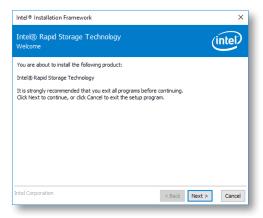

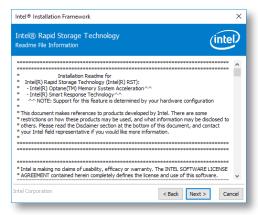

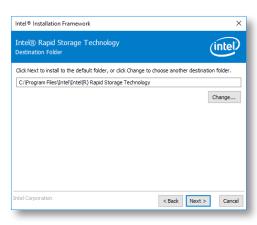

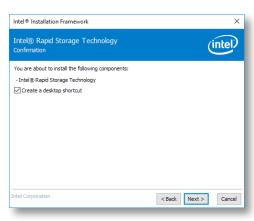

| Intel Rapid Storage Technology              |          |

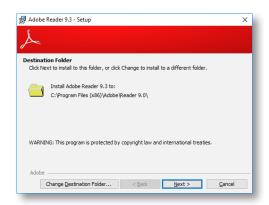

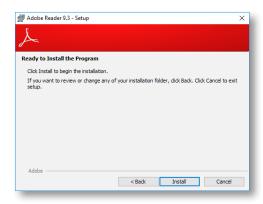

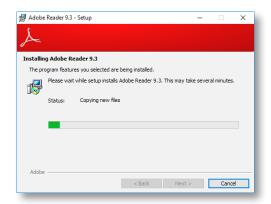

| AUDDE ACTORAL REGUET 9.5                    | 40       |

### **About this Manual**

This manual can be downloaded from the website, or acquired as an electronic file included in the optional CD/DVD. The manual is subject to change and update without notice, and may be based on editions that do not resemble your actual products. Please visit our website or contact our sales representatives for the latest editions.

# Warranty

- Warranty does not cover damages or failures that arised from misuse of the product, inability to use the product, unauthorized replacement or alteration of components and product specifications.

- 2. The warranty is void if the product has been subjected to physical abuse, improper installation, modification, accidents or unauthorized repair of the product.

- Unless otherwise instructed in this user's manual, the user may not, under any circumstances, attempt to perform service, adjustments or repairs on the product, whether in or out of warranty. It must be returned to the purchase point, factory or authorized service agency for all such work.

- 4. We will not be liable for any indirect, special, incidental or consequencial damages to the product that has been modified or altered.

# **Static Electricity Precautions**

It is quite easy to inadvertently damage your PC, system board, components or devices even before installing them in your system unit. Static electrical discharge can damage computer components without causing any signs of physical damage. You must take extra care in handling them to ensure against electrostatic build-up.

- To prevent electrostatic build-up, leave the system board in its anti-static bag until you are ready to install it.

- 2. Wear an antistatic wrist strap.

- 3. Do all preparation work on a static-free surface.

- Hold the device only by its edges. Be careful not to touch any of the components, contacts or connections.

- Avoid touching the pins or contacts on all modules and connectors. Hold modules or connectors by their ends.

#### Important:

Electrostatic discharge (ESD) can damage your processor, disk drive and other components. Perform the upgrade instruction procedures described at an ESD workstation only. If such a station is not available, you can provide some ESD protection by wearing an antistatic wrist strap and attaching it to a metal part of the system chassis. If a wrist strap is unavailable, establish and maintain contact with the system chassis throughout any procedures requiring ESD protection.

# **Safety Measures**

- To avoid damage to the system, use the correct AC input voltage range.

- To reduce the risk of electric shock, unplug the power cord before removing the system chassis cover for installation or servicing. After installation or servicing, cover the system chassis before plugging the power cord.

# **About the Package**

The package contains the following items. If any of these items are missing or damaged, please contact your dealer or sales representative for assistance.

- One SH960MD-CM236/OM170/HM170 board

- · CPU Cooler

# **Optional Items**

- COM332-B carrier board kit

- · Heat spreader

The board and accessories in the package may not come similar to the information listed above. This may differ in accordance with the sales region or models in which it was sold. For more information about the standard package in your region, please contact your dealer or sales representative.

# **Before Using the System Board**

Before using the system board, prepare basic system components. If you are installing the system board in a new system, you will need at least the following internal components.

- Monitor

- USB keyboard

- Storage device such as hard disk drive, CD-ROM, etc.

You will also need external system peripherals you intend to use which will normally include at least a keyboard, a mouse and a video display monitor.

# **Chapter 1 - Introduction**

# **▶** Specifications

| SYSTEM    | Processor       | 6th Generation Intel® Core™ Processors, BGA 1440  - Xeon® E3-1515M v5 Processor, Quad Core, 8M Cache, 2.8GHz (3.7GHz), 45W (Support ECC)  - Core™ i7-6820EQ Processor, Quad Core, 8M Cache, 2.8GHz (3.5GHz), 45W  - Core™ i5-6442EQ Processor, Quad Core, 6M Cache, 1.9GHz (2.7GHz), 25W  - Core™ i3-6100E Processor, Dual Core, 3M Cache, 2.7GHz, 35W (Support ECC)  - Celeron® Processor G3900E, Dual Core, 2M Cache, 2.4GHz, 35W (Support ECC) |

|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Chipset         | Intel® CM236/QM170/HM170                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | Memory          | - 8GB/16GB DDR4 Memory Down<br>- Dual Channel DDR4 2133MHz<br>- ECC (CPU dependent)                                                                                                                                                                                                                                                                                                                                                               |

|           | BIOS            | Insyde SPI 128Mbit                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GRAPHICS  | Controller      | Intel® HD Graphics                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | Feature         | OpenGL up to 4.4, DirectX 12, OpenCL 2.1  HW Decode: AVC/H.264, MPEG2, VC1/WMV9, JPEG/MJPEG, HEVC/H265, VP8, VP9  HW Encode: AVC/H.264, MPEG2, JPEG, HEVC/H265, VP8, VP9                                                                                                                                                                                                                                                                          |

|           | Display         | 1 x VGA/DDI (DDI available upon request) 1 x LVDS/eDP (eDP available upon request) 2 x DDI (HDMI/DVI/DP++)                                                                                                                                                                                                                                                                                                                                        |

|           | Resolution      | VGA: resolution up to 1920x1200 @ 60Hz<br>LVDS: dual channel 24-bit, resolution up to 1920x1200 @ 60Hz<br>HDMI: resolution up to 4096x2160 @ 24Hz or 2560x1600 @ 60Hz<br>DVI: resolution up to 1920x1200 @ 60Hz<br>DP+++/eDP: resolution up to 4096x2304 @ 60Hz                                                                                                                                                                                   |

|           | Triple Displays | VGA + LVDS + DDI, VGA + DDI1 + DDI2<br>eDP + 2 DDI (available upon request)                                                                                                                                                                                                                                                                                                                                                                       |

| EXPANSION | Interface       | 1 x PCle x16 or 2 x PCle x8 (Gen 3)<br>8 x PCle x1 or 2 x PCle x4 or 4 x PCle x2 (Gen 3)<br>1 x LPC<br>1 x I <sup>2</sup> C<br>1 x SMBus<br>2 x UART (TX/RX)                                                                                                                                                                                                                                                                                      |

| AUDIO     | Interface       | HD Audio                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ETHERNET  | Controller      | 1 x Intel <sup>®</sup> I210IT (10/100/1000Mbps)                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1/0               | USB                  | 4 x USB 3.0<br>8 x USB 2.0                                                                                                                                    |

|-------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | SATA                 | 4 x SATA 3.0 (up to 6Gb/s)<br>RAID 0/1/5/10                                                                                                                   |

|                   | DIO                  | 1 x 8-bit DIO                                                                                                                                                 |

| WATCHDOG<br>TIMER | Output &<br>Interval | System Reset, Programmable via Software from 1 to 255 Seconds                                                                                                 |

| SECURITY          | TPM                  | Available Upon Request                                                                                                                                        |

| POWER             | Type                 | 12V, 5VSB, VCC_RTC (ATX mode) 12V, VCC_RTC (AT mode)                                                                                                          |

| OS SUPPORT        |                      | Windows 8.1 64-bit Windows 7 (/WES7) 32/64-bit Windows 10 IoT Enterprise 64-bit Debian 8 (with VESA graphic driver) CentOS 7 (with VESA graphic driver) Linux |

| ENVIRONMENT       | Temperature          | Operating: 0 to 60°C; Storage: -40 to 85°C                                                                                                                    |

|                   | Humidity             | Operating: 5 to 90% RH; Storage: 5 to 90% RH                                                                                                                  |

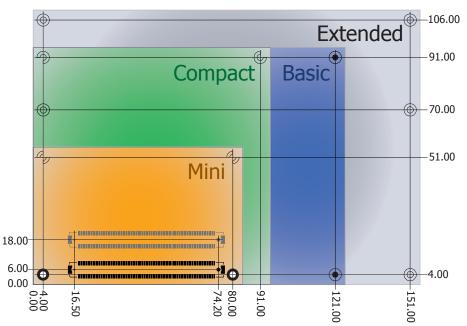

| MECHANICAL        | Dimensions           | COM Express® Basic: 95mm (3.74") x 125mm (4.9")                                                                                                               |

|                   | Compliance           | PICMG COM Express® R2.1, Type 6                                                                                                                               |

#### **▶** Features

### Watchdog Timer

The Watchdog Timer function allows your application to regularly "clear" the system at the set time interval. If the system hangs or fails to function, it will reset at the set time interval so that your system will continue to operate.

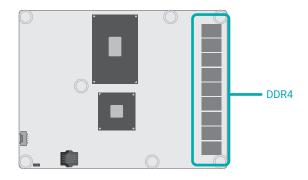

#### DDR4

DDR4 delivers increased system bandwidth and improves performance. The advantages of DDR4 provide an extended battery life and improve the performance at a lower power than DDR3/DDR2. Instead of using memory connectors, the system features memory down with the support of ECC memory.

### **Graphics**

The integrated Intel® HD graphics engine delivers an excellent blend of graphics performance and features to meet business needs. It provides excellent video and 3D graphics with outstanding graphics responsiveness. These enhancements deliver the performance and compatibility needed for today's and tomorrow's business applications. Supports VGA, LVDS, eDP and DDI display outputs.

#### Serial ATA

The system supports multiple SATA 3.0 (up to 6Gb/s) ports and allows for different configurations of RAID levels to meet various requirements for data redundancy and performance.

### Gigabit LAN

The Intel® I210IT Gigabit LAN controller features up to 1Gbps data transmission with support for Intel® Active Management Technology. It provides remote maintenance and manageability for networked computing assets in an enterprise environment.

#### Wake-On-LAN

This feature allows the network to remotely wake up a Soft Power Down (Soft-Off) PC. It is supported via the onboard LAN port or via a PCI LAN card that uses the PCI PME (Power Management Event) signal. However, if your system is in the Suspend mode, you can power-on the system only through an IRQ or DMA interrupt.

#### **USB**

The system board supports the new USB 3.0. It is capable of running at a maximum transmission speed of up to 5 Gbit/s (625 MB/s) and is faster than USB 2.0 (480 Mbit/s, or 60 MB/s) and USB 1.1 (12Mb/s). USB 3.0 reduces the time required for data transmission, reduces power consumption, and is backward compatible with USB 2.0. It is a marked improvement in device transfer speeds between your computer and a wide range of simultaneously accessible external Plug and Play peripherals.

#### **ACPI STR**

The system board is designed to meet the ACPI (Advanced Configuration and Power Interface) specification. ACPI has energy saving features that enables PCs to implement Power Management and Plug-and-Play with operating systems that support OS Direct Power Management. ACPI when enabled in the Power Management Setup will allow you to use the Suspend to RAM function.

With the Suspend to RAM function enabled, you can power-off the system at once by pressing the power button or selecting "Standby" when you shut down Windows® without having to go through the sometimes tiresome process of closing files, applications and operating system. This is because the system is capable of storing all programs and data files during the entire operating session into RAM (Random Access Memory) when it powers-off. The operating session will resume exactly where you left off the next time you power-on the system.

### **Power Failure Recovery**

When power returns after an AC power failure, you may choose to either power-on the system manually or let the system power-on automatically.

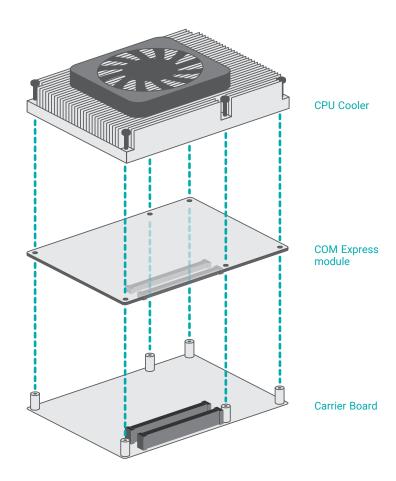

### **▶** Concept

### **COM Express**

Computer-on-module (COM) Express is a PC form factor designed with the core computing integrated on a fairly compact module. All the I/O signals and power supply are concentrated and mapped to the board-to-board connectors on the bottom side to interface with a carrier board that is typically customized to fit the application. When an upgrade or change of application is needed, the physical separation of the core computing and the I/O of COM Express cuts back the cost greatly, whereas canonical IPC designs would typically require an entire makeover. The COM Express module can be replaced when there is only need to upgrade for higher computing performance, while the carrier board can be redesigned when there is solely change in application. COM Express also comes in different form factors and signal Types cut out for different scales and aspects of the system's application. Detailed specifications of COM Express are available on the website of PCI Industrial Computer Manufacturers Group (PICMG).

- O Common for all Form Factors

- Extended only

- Basic only

- **Compact** only

- Compact and Basic only

- Mini only

#### **Carrier Board**

The design of a carrier board for COM Express greatly depends on the form factor and signal Type of the COM Express module. The carrier board typically handles — but not limited to — one COM Express module, and is populated with stand-offs that conform to the form factor of the module's mounting holes.

SH960MD is a Type 6 COM Express (R2.1) module compatible with DFI's proprietary carrier board — COM332-B — as an optional item. If the carrier board is to be customized, the design quide for the carrier board can be attained via the <u>Partner Zone page</u> on our website.

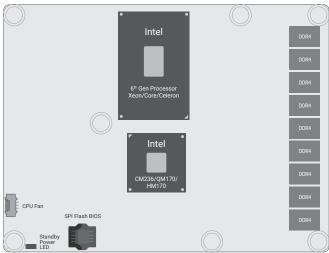

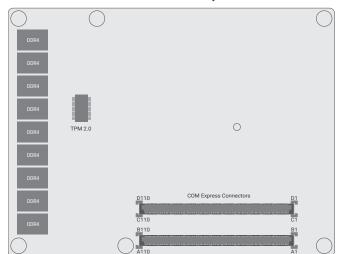

# **Chapter 2 - Hardware Installation**

# **▶** Board Layout

#

###

# \*

#### Important:

Electrostatic discharge (ESD) can damage your board, processor, disk drives, add-in boards, and other components. Perform installation procedures at an ESD workstation only. If such a station is not available, you can provide some ESD protection by wearing an antistatic wrist strap and attaching it to a metal part of the system chassis. If a wrist strap is unavailable, establish and maintain contact with the system chassis throughout any procedures requiring ESD protection.

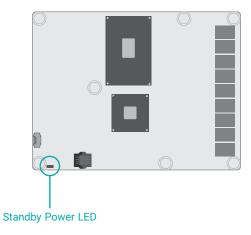

### ► Standby Power LED

#### mportant:

When the Standby Power LED lights red, it indicates that there is power on the system board. Power-off the PC then unplug the power cord prior to installing any devices. Failure to do so will cause severe damage to the motherboard and components.

### System Memory

The system board supports the following memory interface.

#### Single Channel (SC)

Data will be accessed in chunks of 64 bits from the memory channels.

#### Dual Channel (DC)

Data will be accessed in chunks of 128 bits from the memory channels. Dual channel provides better system performance because it doubles the data transfer rate.

Single Channel

DIMMs are on the same channel. DIMMs in a channel can be identical or completely different. However, we highly recommend using

identical DIMMs. Not all slots need to be populated.

**Dual Channel** DIMMs of the same memory configuration are on different channels.

#### Features

- DDR4 2133MHz memory

- ECC (only available with certain options, see <a href="Specifications">Specifications</a>)

- · Dual channel memory interface

# Assembly

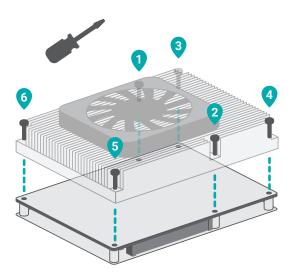

A CPU cooler is included in the standard package. The CPU cooler contains six spring screws and shall be installed after the COM Express module is securely mounted onto the carrier board. Please make sure the cooler, the module, and the carrier board are oriented correctly by inspecting whether the screws, screw holes, and stand-offs all align.

#### Note:

The carrier board is not included in the standard package and is typically customized.

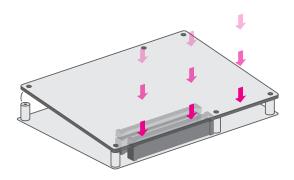

- Locate the COM Express board-to-board connectors on the bottom side of the module and the carrier board. Locate the mounting holes on the module and the corresponding stand-offs on the carrier board.

- A B C

Board-to-board connector on carrier board

2. Place the module on the carrier board while making sure the mounting holes and connectors all align. At the long edge of the module closer to the connector, apply firm pressure onto the module and press it onto the the carrier board until the three standoffs and the edge of the module close up. The other edge of the module away from the connector may still remain slightly aloft from the stand-offs at this moment.

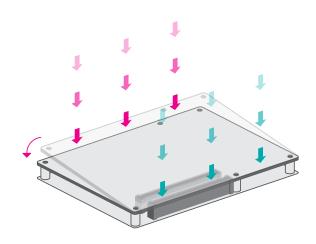

At the long edge away from the connector, apply firm pressure with another hand onto the module and press it onto the carrier board until the module is against the remaining three stand-offs. Please also maintain the pressure described in the previous step the whole time.

#### Assembly

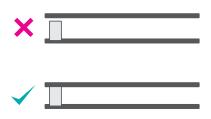

4. Inspect whether the gaps between the module and the stand-offs all close up. It is highly recommended that the module be removed and installed again following the previous steps when there is discernable gap.

5. Place the CPU cooler, i.e. heatsink and fan, onto the module while making sure the screws on the cooler align with the screw holes on the module. The thermal interface metals underneath the cooler should also sit directly on top of the CPU and PCH chipsets on the module. Use a screw driver to fasten the screws in the order as numbered below. By following the order, the risk of damaging the component is significantly reduced.

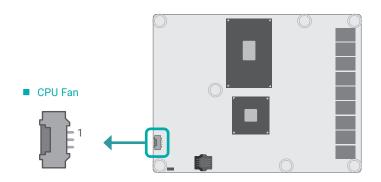

### ► I/O Connectors

#### **CPU Fan**

The fan connector is used to connect to cooling fans. Cooling fans provide adequate air circulation throughout the chassis and dissipate heat to prevent overheating of the system board and components.

#### **BIOS Setting**

Fan speed can be read in the Advanced menu ("SIO ITE8528E" submenu) of the BIOS. Refer to chapter 3 for more information.

### ■ 3-pin Fan Pin Assignment

| Pin | Assignment |  |  |  |

|-----|------------|--|--|--|

| 1   | Ground     |  |  |  |

| 2   | Power      |  |  |  |

| 3   | Sense      |  |  |  |

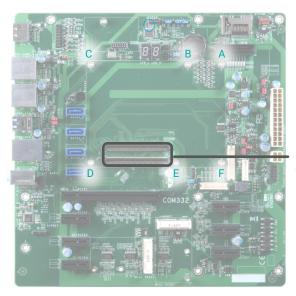

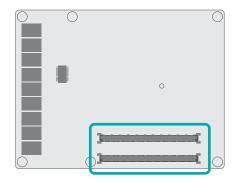

### **Board-to-board Connector**

The two board-to-board connectors are located at the bottom side of the COM Express module. Four rows (row A to row D) of pins and their signal are specified as listed below.

| Row A |                | Row B |             |

|-------|----------------|-------|-------------|

| A1    | GND (FIXED)    | B1    | GND (FIXED) |

| A2    | GBE0_MDI3-     | B2    | GBE0_ACT#   |

| A3    | GBE0_MDI3+     | В3    | LPC_FRAME#  |

| A4    | GBE0_LINK100#  | B4    | LPC_AD0     |

| A5    | GBE0_LINK1000# | B5    | LPC_AD1     |

| A6    | GBE0_MDI2-     | B6    | LPC_AD2     |

| A7    | GBE0_MDI2+     | B7    | LPC_AD3     |

| A8    | GBE0_LINK#     | B8    | LPC_DRQ0#   |

| A9    | GBE0_MDI1-     | B9    | LPC_DRQ1#   |

| A10   | GBE0_MDI1+     | B10   | LPC_CLK     |

| A11   | GND (FIXED)    | B11   | GND (FIXED) |

| A12   | GBE0_MDI0-     | B12   | PWRBTN#     |

| A13   | GBE0_MDI0+     | B13   | SMB_CK      |

| A14   | NC             | B14   | SMB_DAT     |

| A15   | SUS_S3#        | B15   | SMB_ALERT#  |

| A16   | SATA0_TX+      | B16   | SATA1_TX+   |

| A17   | SATA0_TX-      | B17   | SATA1_TX-   |

| A18   | SUS_S4#        | B18   | SUS_STAT#   |

| A19   | SATA0_RX+      | B19   | SATA1_RX+   |

| A20   | SATA0_RX-      | B20   | SATA1_RX-   |

| A21   | GND (FIXED)    | B21   | GND (FIXED) |

| A22   | SATA2_TX+      | B22   | SATA3_TX+   |

| Row A |                          | Row B |               |

|-------|--------------------------|-------|---------------|

| A23   | SATA2_TX-                | B23   | SATA3_TX-     |

| A24   | SUS_S5#                  | B24   | PWR_OK        |

| A25   | SATA2_RX+                | B25   | SATA3_RX+     |

| A26   | SATA2_RX-                | B26   | SATA3_RX-     |

| A27   | BATLOW#                  | B27   | WDT           |

| A28   | (S)ATA_ACT#              | B28   | NC            |

| A29   | AC/HDA_SYNC              | B29   | AC/HDA _SDIN1 |

| A30   | AC/HDA_RST#              | B30   | AC/HDA _SDIN0 |

| A31   | GND (FIXED)              | B31   | GND (FIXED)   |

| A32   | AC/HDA_BITCLK            | B32   | SPKR          |

| A33   | AC/HDA _SDOUT            | B33   | I2C_CK        |

| A34   | BIOS_DISO#               | B34   | I2C_DAT       |

| A35   | THRMTRIP#                | B35   | THRM#         |

| A36   | USB6-                    | B36   | USB7-         |

| A37   | USB6+                    | B37   | USB7+         |

| A38   | USB_6_7_0C#              | B38   | USB_4_5_OC#   |

| A39   | USB4-                    | B39   | USB5-         |

| A40   | USB4+                    | B40   | USB5+         |

| A41   | GND (FIXED)              | B41   | GND (FIXED)   |

| A42   | USB2-                    | B42   | USB3-         |

| A43   | USB2+                    | B43   | USB3+         |

| A44   | USB_2_3_0C#              | B44   | USB_0_1_0C#   |

| A45   | USB0-                    | B45   | USB1-         |

| A46   | USB0+                    | B46   | USB1+         |

| A47   | VCC_RTC                  | B47   | EXCD1_PERST#  |

| A48   | EXCD0_PERST#             | B48   | EXCD1 CPPE#   |

| A49   | EXCD0_CPPE#              | B49   | SYS_RESET#    |

| A50   | LPC_SERIRQ               | B50   | CB_RESET#     |

| A51   | GND (FIXED)              | B51   | GND (FIXED)   |

| A52   | PCIE_TX5+                | B52   | PCIE RX5+     |

| A53   | PCIE_TX5-                | B53   | PCIE_RX5-     |

| A54   | GPI0                     | B54   | GP01          |

| A55   | PCIE_TX4+                | B55   | PCIE RX4+     |

| A56   | PCIE_TX4-                | B56   | PCIE RX4-     |

| A57   | GND                      | B57   | GPO2          |

| A58   | PCIE_TX3+                | B58   | PCIE RX3+     |

| A59   | PCIE_TX3-                | B59   | PCIE_RX3-     |

| A60   | GND (FIXED)              | B60   | GND (FIXED)   |

| A61   | PCIE_TX2+                | B61   | PCIE_RX2+     |

| A62   | PCIE_TX2-                | B62   | PCIE_RX2-     |

| A63   | GPI1                     | B63   | GP03          |

| A64   | PCIE_TX1+                | B64   | PCIE_RX1+     |

| A65   | PCIE_TX1-                | B65   | PCIE_RX1-     |

| A66   | GND                      | B66   | WAKE0#        |

| A67   | GPI2                     | B67   | WAKE1#        |

| A68   | PCIE_TX0+                | B68   | PCIE_RX0+     |

| A69   | PCIE_TX0-                | B69   | PCIE_RX0-     |

| A70   | GND (FIXED)              | B70   | GND (FIXED)   |

| A71   | LVDS_A0+/eDP_TX2+ (opt.) | B71   | LVDS B0+      |

| A72   | LVDS_A0-/eDP_TX2- (opt.) | B72   | LVDS_B0-      |

| A73   | LVDS_A1+/eDP_TX1+ (opt.) | B73   | LVDS_B1+      |

| A74   | LVDS_A1-/eDP_TX1- (opt.) | B74   | LVDS_B1-      |

| A75   | LVDS_A2+/eDP_TX0+ (opt.) | B75   | LVDS_B2+      |

| A76   | LVDS_A2-/eDP_TX0- (opt.) | B76   | LVDS_B2-      |

|       | ,: _:::: (-,-::)         |       |               |

####

| Row A      |                               | Row B |                                     |

|------------|-------------------------------|-------|-------------------------------------|

| A77        | LVDS_VDD_EN/eDP_VDD_EN (opt.) | B77   | LVDS_B3+                            |

| A78        | LVDS_A3+                      | B78   | LVDS_B3-                            |

| A79        | LVDS A3-                      | B79   | LVDS_BKLT_EN/eDP_BKLT_EN (opt.)     |

| A80        | GND (FIXED)                   | B80   | GND (FIXED)                         |

| A81        | LVDS_A_CK+/eDP_TX3+ (opt.)    | B81   | LVDS_B_CK+                          |

| A82        | LVDS_A_CK-/eDP_TX3- (opt.)    | B82   | LVDS_B_CK-                          |

| A83        | LVDS_I2C_CK/eDP_AUX+ (opt.)   | B83   | LVDS_BKLT_CTRL/eDP_BKLT_CTRL (opt.) |

| A84        | LVDS_I2C_DAT/eDP_AUX- (opt.)  | B84   | VCC_5V_SBY                          |

| A85        | GPI3                          | B85   | VCC 5V SBY                          |

| A86        | RSVD                          | B86   | VCC_5V_SBY                          |

| A87        | RSVD/eDP_HPD                  | B87   | VCC_5V_SBY                          |

| A88        | PCIEO_CLK_REF+                | B88   | BIOS DIS1#                          |

| A89        | PCIEO_CLK_REF-                | B89   | VGA_RED                             |

| A90        |                               | B90   |                                     |

|            | GND (FIXED)                   |       | GND (FIXED)                         |

| A91        | SPI_POWER                     | B91   | VGA_GRN                             |

| A92        | SPI_MISO                      | B92   | VGA_BLU                             |

| A93        | GP00                          | B93   | VGA_HSYNC                           |

| A94        | SPI_CLK                       | B94   | VGA_VSYNC                           |

| A95        | SPI_MOSI                      | B95   | VGA_I2C_CK                          |

| A96        | TPM_PP                        | B96   | VGA_I2C_DAT                         |

| A97        | NC                            | B97   | SPI_CS#                             |

| A98        | SER0_TX                       | B98   | RSVD                                |

| A99        | SERO_RX                       | B99   | RSVD                                |

| A100       | GND (FIXED)                   | B100  | GND (FIXED)                         |

| A101       | SER1_TX                       | B101  | FAN_PWMOUT                          |

| A102       | SER1_RX                       | B102  | FAN_TACHIN                          |

| A103       | LID#                          | B103  | SLEEP#                              |

| A104       | VCC_12V                       | B104  | VCC_12V                             |

| A105       | VCC_12V                       | B105  | VCC_12V                             |

| A106       | VCC_12V                       | B106  | VCC_12V                             |

| A107       | VCC_12V                       | B107  | VCC_12V                             |

| A108       | VCC_12V                       | B108  | VCC_12V                             |

| A109       | VCC_12V                       | B109  | VCC_12V                             |

| A110       | GND (FIXED)                   | B110  | GND (FIXED)                         |

| Row C      |                               | Row D |                                     |

| C1         | GND (FIXED)                   | D1    | GND (FIXED)                         |

| C2         | GND                           | D2    | GND                                 |

| C3         | USB_SSRX0-                    | D3    | USB_SSTX0-                          |

| C4         | USB_SSRX0+                    | D4    | USB_SSTX0+                          |

| C5         | GND                           | D5    | GND                                 |

| C6         | USB_SSRX1-                    | D6    | USB_SSTX1-                          |

| C7         | USB_SSRX1+                    | D7    | USB_SSTX1+                          |

| C8         | GND                           | D8    | GND                                 |

| C9         | USB_SSRX2-                    | D8    | USB_SSTX2-                          |

| C10        | USB_SSRX2+                    | D10   | USB_SSTX2+                          |

| C11        | GND (FIXED)                   | D10   | GND (FIXED)                         |

| C12        | USB_SSRX3-                    | D11   | USB_SSTX3-                          |

| C12        |                               | D12   |                                     |

|            | USB_SSRX3+                    |       | USB_SSTX3+                          |

| C14<br>C15 | NC                            | D14   | GND                                 |

| C16        | NC                            | D15   | DDI1_CTRLCLK_AUX+                   |

| C17        | RSVD                          | D16   | DDI1_CTRLDATA_AUX-                  |

| 017        | NOVD                          | D17   | RSVD                                |

| Row C |                    | Row D |                            |

|-------|--------------------|-------|----------------------------|

| C18   | RSVD               | D18   | RSVD                       |

| C19   | PCIE RX6+          | D19   | PCIE_TX6+                  |

| C20   | PCIE_RX6-          | D20   | PCIE_TX6-                  |

| C21   | GND (FIXED)        | D21   | GND (FIXED)                |

| C22   | PCIE_RX7+          | D22   | PCIE TX7+                  |

| C23   | PCIE_RX7-          | D23   | PCIE_TX7-                  |

| C24   | DDI1_HPD           | D23   | RSVD                       |

| C25   | NC                 | D25   | RSVD                       |

| C26   | NC                 | D25   |                            |

| C27   | RSVD               | D27   | DDI1_PAIR0+<br>DDI1_PAIR0- |

|       |                    |       |                            |

| C28   | RSVD               | D28   | RSVD                       |

| C29   | NC NO              | D29   | DDI1_PAIR1+                |

| C30   | NC                 | D30   | DDI1_PAIR1-                |

| C31   | GND (FIXED)        | D31   | GND (FIXED)                |

| C32   | DDI2_CTRLCLK_AUX+  | D32   | DDI1_PAIR2+                |

| C33   | DDI2_CTRLDATA_AUX- | D33   | DDI1_PAIR2-                |

| C34   | DDI2_DDC_AUX_SEL   | D34   | DDI1_DDC_AUX_SEL           |

| C35   | RSVD               | D35   | RSVD                       |

| C36   | DDI3_CTRLCLK_AUX+  | D36   | DDI1_PAIR3+                |

| C37   | DDI3_CTRLDATA_AUX- | D37   | DDI1_PAIR3-                |

| C38   | DDI3_DDC_AUX_SEL   | D38   | RSVD                       |

| C39   | DDI3_PAIR0+        | D39   | DDI2_PAIR0+                |

| C40   | DDI3_PAIR0-        | D40   | DDI2_PAIR0-                |

| C41   | GND (FIXED)        | D41   | GND (FIXED)                |

| C42   | DDI3_PAIR1+        | D42   | DDI2_PAIR1+                |

| C43   | DDI3_PAIR1-        | D43   | DDI2_PAIR1-                |

| C44   | DDI3_HPD           | D44   | DDI2_HPD                   |

| C45   | RSVD               | D45   | RSVD                       |

| C46   | DDI3_PAIR2+        | D46   | DDI2_PAIR2+                |

| C47   | DDI3_PAIR2-        | D47   | DDI2_PAIR2-                |

| C48   | RSVD               | D48   | RSVD                       |

| C49   | DDI3_PAIR3+        | D49   | DDI2_PAIR3+                |

| C50   | DDI3_PAIR3-        | D50   | DDI2_PAIR3-                |

| C51   | GND (FIXED)        | D51   | GND (FIXED)                |

| C52   | PEG_RX0+           | D52   | PEG_TX0+                   |

| C53   | PEG_RX0-           | D53   | PEG_TX0-                   |

| C54   | NC                 | D54   | PEG_LANE_RV#               |

| C55   | PEG_RX1+           | D55   | PEG_TX1+                   |

| C56   | PEG_RX1-           | D56   | PEG_TX1-                   |

| C57   | NC                 | D57   | GND                        |

| C58   | PEG_RX2+           | D58   | PEG_TX2+                   |

| C59   | PEG RX2-           | D59   | PEG TX2-                   |

| C60   | GND (FIXED)        | D60   | GND (FIXED)                |

| C61   | PEG_RX3+           | D61   | PEG_TX3+                   |

| C62   | PEG_RX3-           | D62   | PEG_TX3-                   |

| C63   | RSVD               | D63   | RSVD                       |

| C64   | RSVD               | D64   | RSVD                       |

| C65   | PEG RX4+           | D65   | PEG_TX4+                   |

| C66   | PEG_RX4-           | D66   | PEG_TX4-                   |

| C67   | NC                 | D67   | GND                        |

| C68   | PEG_RX5+           | D68   | PEG_TX5+                   |

| C69   | PEG_RX5+           | D69   | PEG_TX5-                   |

| C70   | GND (FIXED)        | D70   | GND (FIXED)                |

| C71   |                    | D70   |                            |

| 0/1   | PEG_RX6+           | ווע   | PEG_TX6+                   |

I/O Connectors

**▶** Board-to-board Connector

| Row C |             | Row D |             |

|-------|-------------|-------|-------------|

| C72   | PEG_RX6-    | D72   | PEG_TX6-    |

| C73   | GND         | D73   | GND         |

| C74   | PEG_RX7+    | D74   | PEG_TX7+    |

| C75   | PEG RX7-    | D75   | PEG TX7-    |

| C76   | GND         | D76   | GND         |

| C77   | RSVD        | D77   | RSVD        |

| C78   | PEG_RX8+    | D78   | PEG_TX8+    |

| C79   | PEG_RX8-    | D79   | PEG_TX8-    |

| C80   | GND (FIXED) | D80   | GND (FIXED) |

| C81   | PEG_RX9+    | D81   | PEG_TX9+    |

| C82   | PEG_RX9-    | D82   | PEG_TX9-    |

| C83   | RSVD        | D83   | RSVD        |

| C84   | GND         | D84   | GND         |

| C85   | PEG_RX10+   | D85   | PEG_TX10+   |

| C86   | PEG_RX10-   | D86   | PEG_TX10-   |

| C87   | GND         | D87   | GND         |

| C88   | PEG_RX11+   | D88   | PEG_TX11+   |

| C89   | PEG_RX11-   | D89   | PEG_TX11-   |

| C90   | GND (FIXED) | D90   | GND (FIXED) |

| C91   | PEG_RX12+   | D91   | PEG_TX12+   |

| C92   | PEG_RX12-   | D92   | PEG_TX12-   |

| C93   | GND         | D93   | GND         |

| C94   | PEG_RX13+   | D94   | PEG_TX13+   |

| C95   | PEG_RX13-   | D95   | PEG_TX13-   |

| C96   | GND         | D96   | GND         |

| C97   | RSVD        | D97   | RSVD        |

| C98   | PEG_RX14+   | D98   | PEG_TX14+   |

| C99   | PEG_RX14-   | D99   | PEG_TX14-   |

| C100  | GND (FIXED) | D100  | GND (FIXED) |

| C101  | PEG_RX15+   | D101  | PEG_TX15+   |

| C102  | PEG_RX15-   | D102  | PEG_TX15-   |

| C103  | GND         | D103  | GND         |

| C104  | VCC_12V     | D104  | VCC_12V     |

| C105  | VCC_12V     | D105  | VCC_12V     |

| C106  | VCC_12V     | D106  | VCC_12V     |

| C107  | VCC_12V     | D107  | VCC_12V     |

| C108  | VCC_12V     | D108  | VCC_12V     |

| C109  | VCC_12V     | D109  | VCC_12V     |

| C110  | GND (FIXED) | D110  | GND (FIXED) |

|       |             |       |             |

# **▶** Signal Descriptions

### Pin Types

Input to the Module 0

Output from the Module Bi-directional input / output signal 1/0

Open drain output

RSVD pins are reserved for future use and should be no connect. Do not tie the RSVD pins together.

**HDA Signals Descriptions**

| Pin# | Pin Type                     | Pwr Rail /Tolerance                                                                                                                                                                                       | SH960MD PU/PD                                                                                                                                                                                                                                                                                                                                                             | Module Base Specification R2.1 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | COM Express Carrier Design Guide R2.0 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A30  | O CMOS                       | 3.3V Suspend/3.3V                                                                                                                                                                                         | series 33Ω resistor                                                                                                                                                                                                                                                                                                                                                       | Reset output to CODEC, active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CODEC Reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A29  | O CMOS                       | 3.3V/3.3V                                                                                                                                                                                                 | series 33Ω resistor                                                                                                                                                                                                                                                                                                                                                       | Sample-synchronization signal to the CODEC(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Serial Sample Rate Synchronization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A32  | I/O CMOS                     | 3.3V/3.3V                                                                                                                                                                                                 | series 33Ω resistor                                                                                                                                                                                                                                                                                                                                                       | Serial data clock generated by the external CODEC(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24 MHz Serial Bit Clock for HDA CODEC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A33  | O CMOS                       | 3.3V/3.3V                                                                                                                                                                                                 | series 33Ω resistor                                                                                                                                                                                                                                                                                                                                                       | Serial TDM data output to the CODEC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Audio Serial Data Output Stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| B30  | I/O CMOS                     | 3.3V Suspend/3.3V                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                           | Serial TDM data inputs from up to 3 CODECs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Audio Serial Data Input Stream from CODEC[0:2].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B29  | I/O CMOS                     | 3.3V Suspend/3.3V                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B28  | I/O CMOS                     | 3.3V Suspend/3.3V                                                                                                                                                                                         | NC                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | Pin# A30 A29 A32 A33 B30 B29 | Pin#         Pin Type           A30         O CMOS           A29         O CMOS           A32         I/O CMOS           A33         O CMOS           B30         I/O CMOS           B29         I/O CMOS | Pin#         Pin Type         Pwr Rail /Tolerance           A30         0 CMOS         3.3V Suspend/3.3V           A29         0 CMOS         3.3V/3.3V           A32         I/O CMOS         3.3V/3.3V           A33         0 CMOS         3.3V/3.3V           B30         I/O CMOS         3.3V Suspend/3.3V           B29         I/O CMOS         3.3V Suspend/3.3V | Pin#         Pin Type         Pwr Rail / Tolerance         SH960MD PU/PD           A30         0 CMOS         3.3V Suspend/3.3V         series 33Ω resistor           A29         0 CMOS         3.3V/3.3V         series 33Ω resistor           A32         I/0 CMOS         3.3V/3.3V         series 33Ω resistor           A33         0 CMOS         3.3V/3.3V         series 33Ω resistor           B30         I/0 CMOS         3.3V Suspend/3.3V           B29         I/0 CMOS         3.3V Suspend/3.3V | Pin#Pin TypePwr Rail /ToleranceSH960MD PU/PDModule Base Specification R2.1 DescriptionA300 CM0S3.3V Suspend/3.3Vseries 33Ω resistorReset output to CODEC, active low.A290 CM0S3.3V/3.3Vseries 33Ω resistorSample-synchronization signal to the CODEC(s).A32 $1/0$ CM0S3.3V/3.3Vseries 33Ω resistorSerial data clock generated by the external CODEC(s).A330 CM0S3.3V/3.3Vseries 33Ω resistorSerial TDM data output to the CODEC.B30 $1/0$ CM0S3.3V Suspend/3.3VSerial TDM data inputs from up to 3 CODECs.B29 $1/0$ CM0S3.3V Suspend/3.3V |

| Signal             | Pin# | Pin Type   | Pwr Rail /Tolerance | SH960MD PU/PD | Module Base Specification R2.1 Description                                                                                                                                                                                                                                                                                                                                        | COM Express Carrier Design Guide R2.0 Description                            |

|--------------------|------|------------|---------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| GBE0_MDI0+         | A13  | I/O Analog | 3.3V max Suspend    |               | Gigabit Ethernet Controller 0: Media Dependent Interface Differential                                                                                                                                                                                                                                                                                                             | Media Dependent Interface (MDI) differential pair 0.                         |

| GBE0_MDI0-         | A12  | I/O Analog | 3.3V max Suspend    |               | Pairs 0,1,2,3. The MDI can operate in 1000, 100 and 10 Mbit / sec<br>— modes. Some pairs are unused in some modes, per the following:                                                                                                                                                                                                                                             |                                                                              |

| GBE0_MDI1+         | A10  | I/O Analog | 3.3V max Suspend    |               | 1000BASE-T 100BASE-TX 10BASE-T                                                                                                                                                                                                                                                                                                                                                    | Media Dependent Interface (MDI) differential pair 1.                         |

| GBE0_MDI1-         | A9   | I/O Analog | 3.3V max Suspend    |               | $MDI[0]+/ B1_DA+/ TX+/ TX+/-$                                                                                                                                                                                                                                                                                                                                                     |                                                                              |

| GBE0_MDI2+         | A7   | I/O Analog | 3.3V max Suspend    |               | MDI[1]+/- B1_DB+/- RX+/- RX+/-<br>                                                                                                                                                                                                                                                                                                                                                | Media Dependent Interface (MDI) differential pair 2.                         |

| GBE0_MDI2-         | A6   | I/O Analog | 3.3V max Suspend    |               | MDI[3]+/- B1_DD+/-                                                                                                                                                                                                                                                                                                                                                                | Only used for 1000Mbit/sec Gigabit Ethernet mode.                            |

| GBE0_MDI3+         | A3   | I/O Analog | 3.3V max Suspend    |               |                                                                                                                                                                                                                                                                                                                                                                                   | Media Dependent Interface (MDI) differential pair 3.                         |

| GBE0_MDI3-         | A2   | I/O Analog | 3.3V max Suspend    |               |                                                                                                                                                                                                                                                                                                                                                                                   | Only used for 1000Mbit/sec Gigabit Ethernet mode.                            |

| GBE0_ACT#          | B2   | OD CMOS    | 3.3V Suspend/3.3V   |               | Gigabit Ethernet Controller 0 activity indicator, active low.                                                                                                                                                                                                                                                                                                                     | Ethernet controller 0 activity indicator, active low.                        |

| GBE0_LINK#         | A8   | OD CMOS    | 3.3V Suspend/3.3V   |               | Gigabit Ethernet Controller 0 link indicator, active low.                                                                                                                                                                                                                                                                                                                         | Ethernet controller 0 link indicator, active low.                            |

| GBE0_<br>LINK100#  | A4   | OD CMOS    | 3.3V Suspend/3.3V   |               | Gigabit Ethernet Controller 0 100 Mbit / sec link indicator, active low.                                                                                                                                                                                                                                                                                                          | Ethernet controller 0 100Mbit/sec link indicator, active low.                |

| GBE0_<br>LINK1000# | A5   | OD CMOS    | 3.3V Suspend/3.3V   |               | Gigabit Ethernet Controller 0 1000 Mbit / sec link indicator, active low.                                                                                                                                                                                                                                                                                                         | Ethernet controller 0 1000Mbit/sec link indicator, active low.               |

| GBE0_CTREF         | A14  | REF        | GND min 3.3V max    | NC            | Reference voltage for Carrier Board Ethernet channel 0 magnetics center tap. The reference voltage is determined by the requirements of the Module PHY and may be as low as 0V and as high as 3.3V. The reference voltage output shall be current limited on the Module. In the case in which the reference is shorted to ground, the current shall be limited to 250 mA or less. | Reference voltage for Carrier Board Ethernet channel 0 magnetics center tap. |

| Signal      | Pin# | Pin Type | Pwr Rail /Tolerance  | SH960MD PU/PD         | Module Base Specification R2.1 Description                       | COM Express Carrier Design Guide R2.0 Description                                       |

|-------------|------|----------|----------------------|-----------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| SATA0_TX+   | A16  | O SATA   | AC coupled on Module | AC Coupling capacitor | Serial ATA or SAS Channel 0 transmit differential pair.          | Serial ATA channel 0<br>Transmit output differential pair.                              |

| SATA0_TX-   | A17  | O SATA   | AC coupled on Module | AC Coupling capacitor |                                                                  |                                                                                         |

| SATA0_RX+   | A19  | I SATA   | AC coupled on Module | AC Coupling capacitor | Serial ATA or SAS Channel 0 receive differential pair.           | Serial ATA channel 0<br>Receive input differential pair.                                |

| SATA0_RX-   | A20  | I SATA   | AC coupled on Module | AC Coupling capacitor |                                                                  |                                                                                         |

| SATA1_TX+   | B16  | O SATA   | AC coupled on Module | AC Coupling capacitor | Serial ATA or SAS Channel 1 transmit differential pair.          | Serial ATA channel 1<br>Transmit output differential pair.                              |

| SATA1_TX-   | B17  | O SATA   | AC coupled on Module | AC Coupling capacitor |                                                                  |                                                                                         |

| SATA1_RX+   | B19  | ISATA    | AC coupled on Module | AC Coupling capacitor | Serial ATA or SAS Channel 1 receive differential pair.           | Serial ATA channel 1<br>Receive input differential pair.                                |

| SATA1_RX-   | B20  | I SATA   | AC coupled on Module | AC Coupling capacitor |                                                                  |                                                                                         |

| SATA2_TX+   | A22  | O SATA   | AC coupled on Module | AC Coupling capacitor | Serial ATA or SAS Channel 2 transmit differential pair.          | Serial ATA channel 2<br>Transmit output differential pair.                              |

| SATA2_TX-   | A23  | O SATA   | AC coupled on Module | AC Coupling capacitor |                                                                  |                                                                                         |

| SATA2_RX+   | A25  | I SATA   | AC coupled on Module | AC Coupling capacitor | Serial ATA or SAS Channel 2 receive differential pair.           | Serial ATA channel 2<br>Receive input differential pair.                                |

| SATA2_RX-   | A26  | I SATA   | AC coupled on Module | AC Coupling capacitor |                                                                  |                                                                                         |

| SATA3_TX+   | B22  | O SATA   | AC coupled on Module | AC Coupling capacitor | Serial ATA or SAS Channel 3 transmit differential pair.          | Serial ATA channel 3<br>Transmit output differential pair.                              |

| SATA3_TX-   | B23  | O SATA   | AC coupled on Module | AC Coupling capacitor |                                                                  |                                                                                         |

| SATA3_RX+   | B25  | I SATA   | AC coupled on Module | AC Coupling capacitor | Serial ATA or SAS Channel 3 receive differential pair.           | Serial ATA channel 3<br>Receive input differential pair.                                |

| SATA3_RX-   | B26  | I SATA   | AC coupled on Module | AC Coupling capacitor |                                                                  |                                                                                         |

| (S)ATA_ACT# | A28  | I/O CMOS | 3.3V / 3.3V          | PU 10KW to 3.3V       | ATA (parallel and serial) or SAS activity indicator, active low. | Serial ATA activity LED. Open collector output pin driven during SATA command activity. |

| Signal            | Pin# | Pin Type | Pwr Rail /Tolerance   | SH960MD PU/PD | Module Base Specification R2.1 Description                                 | COM Express Carrier Design Guide R2.0 Description                       |

|-------------------|------|----------|-----------------------|---------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|

| PCIE_TX0+         | A68  | O PCIE   | AC coupled on Module  |               | PCI Express Differential Transmit Pairs 0                                  | PCIe channel 0. Transmit Output differential pair.                      |

| PCIE_TX0-         | A69  |          |                       | capacitor     |                                                                            |                                                                         |

| PCIE_RX0+         | B68  | I PCIE   | AC coupled off Module |               | PCI Express Differential Receive Pairs 0                                   | PCIe channel 0. Receive Input differential pair.                        |

| PCIE_RX0-         | B69  |          |                       |               |                                                                            |                                                                         |

| PCIE_TX1+         | A64  | O PCIE   | AC coupled on Module  |               | PCI Express Differential Transmit Pairs 1                                  | PCIe channel 1. Transmit Output differential pair.                      |

| PCIE_TX1-         | A65  |          |                       | capacitor     |                                                                            |                                                                         |

| PCIE_RX1+         | B64  | I PCIE   | AC coupled off Module |               | PCI Express Differential Receive Pairs 1                                   | PCIe channel 1. Receive Input differential pair.                        |