# **EPX-EHLP**

Intel® Elkhart Lake 2.5" Pico ITX motherboard

# **User's Manual**

2<sup>nd</sup> Ed – 10 February 2023

Part No. E2047EPHP01R

#### **FCC Statement**

THIS DEVICE COMPLIES WITH PART 15 FCC RULES. OPERATION IS SUBJECT TO THE FOLLOWING TWO CONDITIONS:

- (1) THIS DEVICE MAY NOT CAUSE HARMFUL INTERFERENCE.

- (2) THIS DEVICE MUST ACCEPT ANY INTERFERENCE RECEIVED INCLUDING INTERFERENCE THAT MAY CAUSE UNDESIRED OPERATION.

THIS EQUIPMENT HAS BEEN TESTED AND FOUND TO COMPLY WITH THE LIMITS FOR A CLASS "A" DIGITAL DEVICE, PURSUANT TO PART 15 OF THE FCC RULES.

THESE LIMITS ARE DESIGNED TO PROVIDE REASONABLE PROTECTION AGAINST HARMFUL INTERFERENCE WHEN THE EQUIPMENT IS OPERATED IN A COMMERCIAL ENVIRONMENT. THIS EQUIPMENT GENERATES, USES, AND CAN RADIATE RADIO FREQUENCY ENERGY AND, IF NOT INSTALLED AND USED IN ACCORDANCE WITH THE INSTRUCTION MANUAL, MAY CAUSE HARMFUL INTERFERENCE TO RADIO COMMUNICATIONS.

OPERATION OF THIS EQUIPMENT IN A RESIDENTIAL AREA IS LIKELY TO CAUSE HARMFUL INTERFERENCE IN WHICH CASE THE USER WILL BE REQUIRED TO CORRECT THE INTERFERENCE AT HIS OWN EXPENSE.

#### **Notice**

This guide is designed for experienced users to setup the system within the shortest time. For detailed information, please always refer to the electronic user's manual.

# **Copyright Notice**

Copyright © 2023 Avalue Technology Inc., ALL RIGHTS RESERVED.

No part of this document may be reproduced, copied, translated, or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the prior written permission of the original manufacturer.

# **Trademark Acknowledgement**

Brand and product names are trademarks or registered trademarks of their respective owners.

#### **Disclaimer**

Avalue Technology Inc. reserves the right to make changes, without notice, to any product, including circuits and/or software described or contained in this manual in order to improve design and/or performance. Avalue Technology assumes no responsibility or liability for the use of the described product(s), conveys no license or title under any patent, copyright, or masks work rights to these products, and makes no representations or warranties that

2 EPX-EHLP User's Manual

these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described in this manual are for illustration purposes only. Avalue Technology Inc. makes no representation or warranty that such application will be suitable for the specified use without further testing or modification.

## **Life Support Policy**

Avalue Technology's PRODUCTS ARE NOT FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE PRIOR WRITTEN APPROVAL OF Avalue Technology Inc.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into body, or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## A Message to the Customer

#### **Avalue Customer Services**

Each and every Avalue's product is built to the most exacting specifications to ensure reliable performance in the harsh and demanding conditions typical of industrial environments. Whether your new Avalue device is destined for the laboratory or the factory floor, you can be assured that your product will provide the reliability and ease of operation for which the name Avalue has come to be known.

Your satisfaction is our primary concern. Here is a guide to Avalue's customer services. To ensure you get the full benefit of our services, please follow the instructions below carefully.

# **Technical Support**

We want you to get the maximum performance from your products. So if you run into technical difficulties, we are here to help. For the most frequently asked questions, you can easily find answers in your product documentation. These answers are normally a lot more detailed than the ones we can give over the phone. So please consult the user's manual first.

To receive the latest version of the user's manual; please visit our Web site at: <a href="http://www.avalue.com.tw/">http://www.avalue.com.tw/</a>

# EPX-EHLP User's Manual Product Warranty

Avalue warrants to you, the original purchaser, that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products which have been repaired or altered by persons other than repair personnel authorized by Avalue, or which have been subject to misuse, abuse, accident or improper installation. Avalue assumes no liability under the terms of this warranty as a consequence of such events. Because of Avalue's high quality-control standards and rigorous testing, most of our customers never need to use our repair service. If any of Avalue's products is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, you will be billed according to the cost of replacement materials, service time, and freight. Please consult your dealer for more details. If you think you have a defective product, follow these steps:

- 1. Collect all the information about the problem encountered. (For example, CPU type and speed, Avalue's products model name, hardware & BIOS revision number, other hardware and software used, etc.) Note anything abnormal and list any on-screen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information available.

- 3. If your product is diagnosed as defective, obtain an RMA (return material authorization) number from your dealer. This allows us to process your good return more quickly.

- 4. Carefully pack the defective product, a complete Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

# **Content**

| 1.  | Ge     | tting    | Started                            | 8  |

|-----|--------|----------|------------------------------------|----|

| 1.1 | 9      | Safety   | Precautions                        | 8  |

| 1.2 | F      | Packin   | g List                             | 8  |

| 1.3 |        | Docum    | ent Amendment History              | 9  |

| 1.4 |        | Manua    | l Objectives                       | 10 |

| 1.5 |        | Systen   | n Specifications                   | 11 |

| 1.6 | . /    | 4rchite  | cture Overview—Block Diagram       | 15 |

| 2.  | На     | rdwar    | e Configuration                    | 16 |

| 2.1 | F      | Produc   | ct Overview                        | 17 |

| 2.2 |        | Jumpe    | r and Connector List               | 18 |

| 2.3 |        | Setting  | Jumpers & Connectors               | 20 |

| 2   | 2.3.1  | AT/A     | TX mode selector (AT_CMOS1)        | 20 |

| 2   | 2.3.2  | JESP     | l connector (JESPI 1)              | 20 |

| 2   | 2.3.3  | Gene     | ral purpose I/O connector (JDIO1)  | 21 |

| 2   | 2.3.4  | Misce    | ellaneous setting connector (JFP1) | 21 |

| 2   | 2.3.5  | Seria    | Port 1 connector (JCOM1)           | 22 |

| 2   | 2.3.6  | Seria    | Port 2 connector (JCOM2)           | 22 |

| 2   | 2.3.7  | USB      | connector (JUSB 1)                 | 23 |

| 2   | 2.3.8  | SPI h    | eader (JSPI_EC1)                   | 23 |

| 2   | 2.3.9  | Batte    | ry connector (BT1)                 | 24 |

| 2   | 2.3.10 | LVDS     | S connector (JLVDS1)               | 25 |

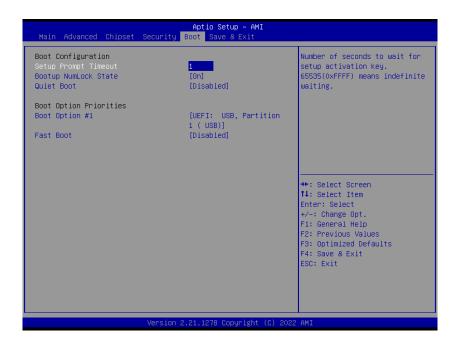

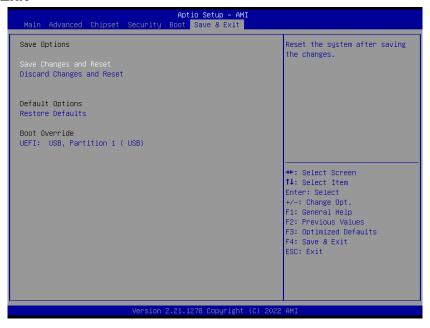

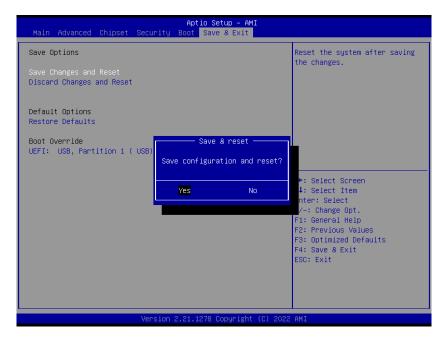

| 3.E | BIOS   | Setup    | <b>)</b>                           | 26 |

| 3.1 | I      | ntrodu   | ction                              | 27 |

| 3.2 |        | Startin  | g Setup                            | 27 |

| 3.3 | ι      | Jsing \$ | Setup                              | 28 |

| 3.4 | . (    | Getting  | y Help                             | 29 |

| 3.5 | I      | n Cas    | e of Problems                      | 29 |

| 3.6 | E      | BIOS s   | setup                              | 30 |

| 3   | 3.6.1  | Main     | Menu                               | 30 |

|     | 3.6    | .1.1     | System Language                    | 31 |

|     | 3.6    | .1.2     | System Date                        | 31 |

|     | 3.6    | .1.3     | System Time                        | 31 |

| 3   | 3.6.2  | Adva     | nced Menu                          | 31 |

|     | 3.6    | .2.1     | CPU Configuration                  | 32 |

|     | 3.6    | .2.2     | Power & Performance                | 32 |

|     | 3.6    | .2.2.1   | CPU - Power Management Control     | 33 |

|     | 3.6    | .2.2.2   | GT - Power Management Control      | 34 |

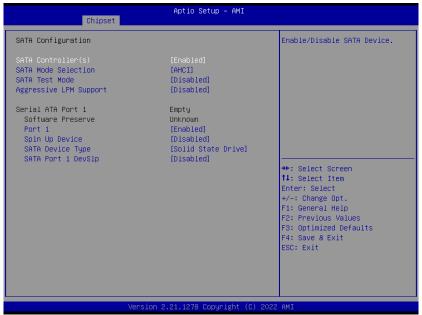

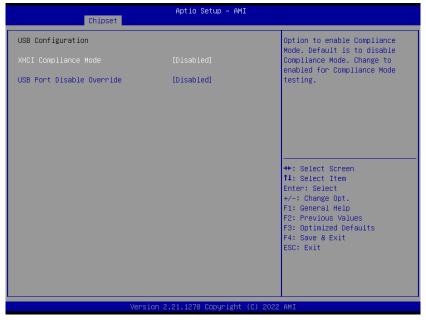

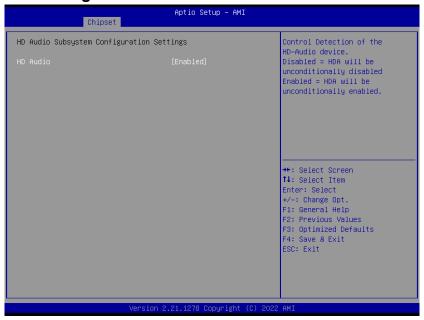

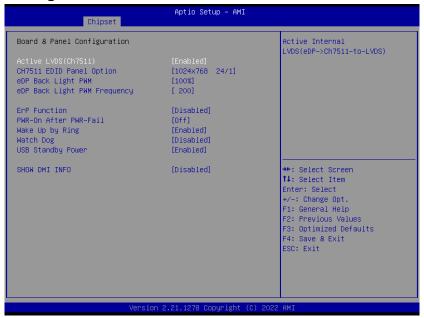

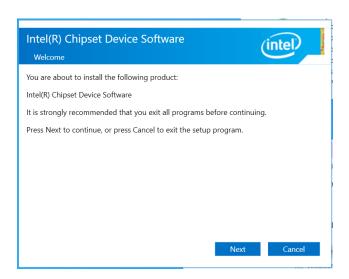

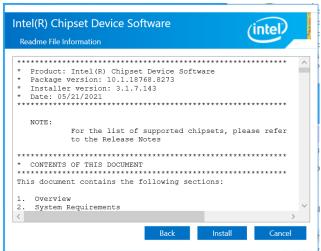

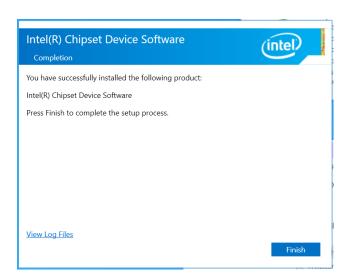

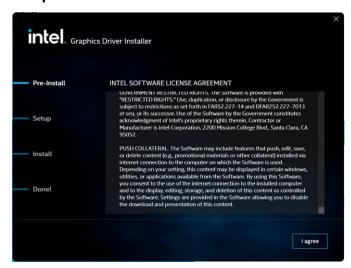

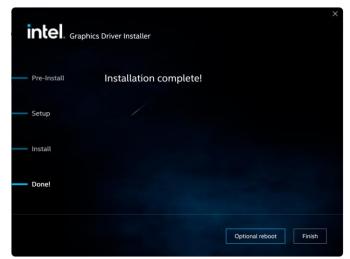

#### **EPX-EHLP User's Manual** 3.6.2.3 3.6.2.3.1 PTT Configuration.......36 3.6.2.3.2 3.6.2.4 3.6.2.5 3.6.2.6 3.6.2.6.1 3.6.2.6.2 3.6.2.7 3.6.2.8 3.6.2.9 3.6.2.10 3.6.2.11 3.6.2.12 3.6.3 3.6.3.1 3.6.3.1.1 3.6.3.1.2 3.6.3.2 3.6.3.2.1 3.6.3.2.2 3.6.3.2.3 HD Audio Configuration ...... 52 3.6.3.2.4 3.6.3.3 Security .......54 3.6.4 3.6.4.1 3.6.5 3.6.6 3.6.6.1 Save Changes and Reset......57 3.6.6.2 3.6.6.3 3.6.6.4 4. Drivers Installation......59 4.1 Install Chipset Driver......60 4.2 Install VGA Driver.....61

|       |                         | User's Manual |

|-------|-------------------------|---------------|

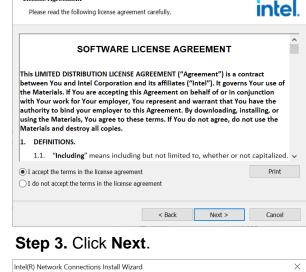

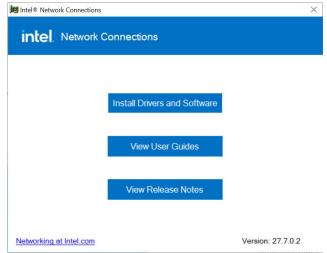

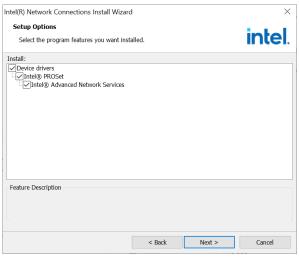

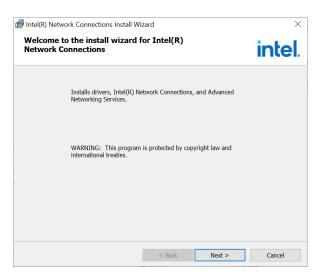

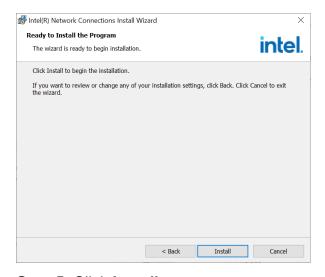

| 4.3   | Install Ethernet Driver | 62            |

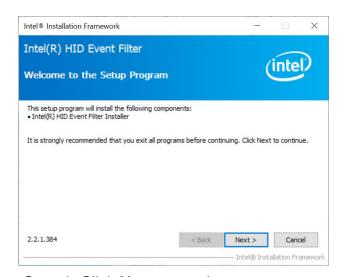

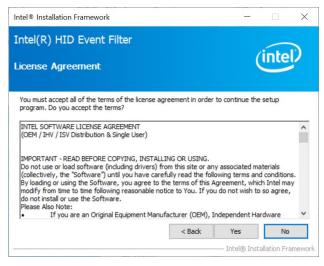

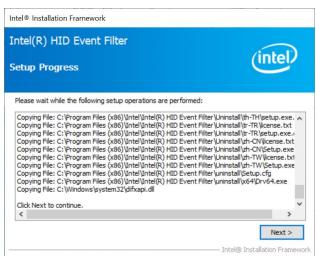

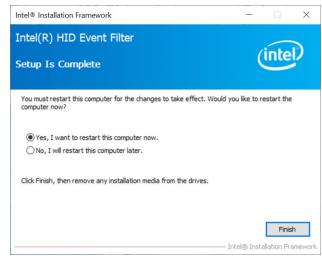

| 4.4   | Install HID Driver      | 64            |

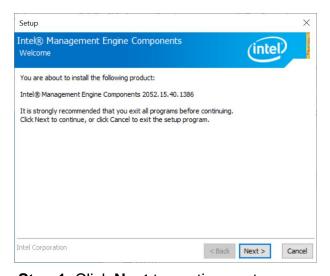

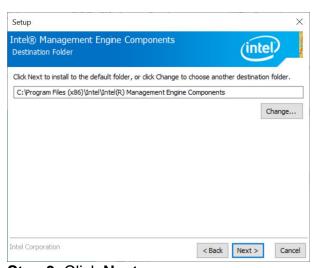

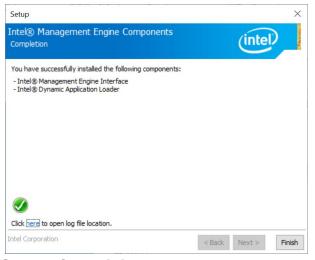

| 4.5   | Install ME Driver       | 65            |

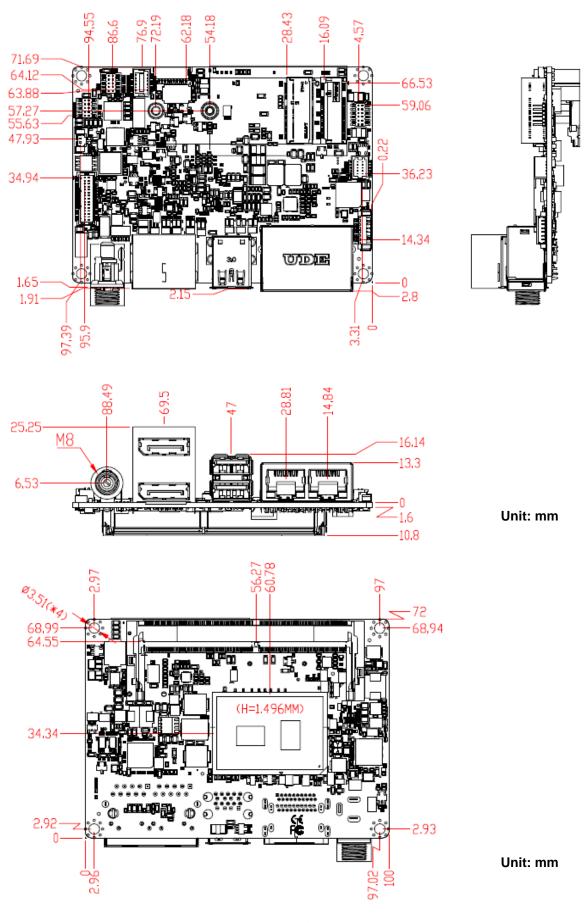

| 5. Me | echanical Drawing       | 66            |

# 1. Getting Started

# 1.1 Safety Precautions

#### Warning!

Always completely disconnect the power cord from your chassis whenever you work with the hardware. Do not make connections while the power is on. Sensitive electronic components can be damaged by sudden power surges. Only experienced electronics personnel should open the PC chassis.

#### Caution!

Always ground yourself to remove any static charge before touching the CPU card. Modern electronic devices are very sensitive to static electric charges. As a safety precaution, use a grounding wrist strap at all times. Place all electronic components in a static-dissipative surface or static-shielded bag when they are not in the chassis.

# 1.2 Packing List

Before you begin installing your single board, please make sure that the following materials have been shipped:

1 x EPX-EHLP motherboard

If any of the above items is damaged or missing, contact your retailer.

# 1.3 Document Amendment History

| Revision        | Date          | Ву     | Comment                      |

|-----------------|---------------|--------|------------------------------|

| 1 <sup>st</sup> | January 2023  | Avalue | Initial Release              |

| 2 <sup>nd</sup> | February 2023 | Avalue | Update System Specifications |

## 1.4 Manual Objectives

This manual describes in details Avalue Technology EPX-EHLP Single Board.

We have tried to include as much information as possible but we have not duplicated information that is provided in the standard IBM Technical References, unless it proved to be necessary to aid in the understanding of this board.

We strongly recommend that you study this manual carefully before attempting to set up EPX-EHLP or change the standard configurations. Whilst all the necessary information is available in this manual we would recommend that unless you are confident, you contact your supplier for guidance.

Please be aware that it is possible to create configurations within the CMOS RAM that make booting impossible. If this should happen, clear the CMOS settings, (see the description of the Jumper Settings for details).

If you have any suggestions or find any errors regarding this manual and want to inform us of these, please contact our Customer Service department with the relevant details.

| EPX-EHLP             |                                                                                |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------|--|--|--|--|

|                      | Intel® Atom® x6000E Series and Celeron® J Series processors with CPU           |  |  |  |  |

|                      | Bottom Mounted                                                                 |  |  |  |  |

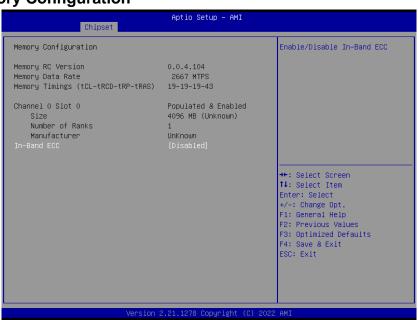

|                      | One 260-pin DDR4 2666MHz SO-DIMM socket, supports up to 32GB Max (Only         |  |  |  |  |

|                      | Atom® x6000 Series Processors support IBECC)                                   |  |  |  |  |

|                      | 2 x Intel® I225/i226LM(I225/i226IT for wide temp version) 2.5 Gigabit Ethernet |  |  |  |  |

|                      | 1 x Dual stack DP(Upper DP, Lower DP++), 1CH LVDS                              |  |  |  |  |

|                      | 4 x USB 2.0 by pin header                                                      |  |  |  |  |

| Product Features     | 2 x USB 3.1 Gen2 at I/O                                                        |  |  |  |  |

|                      | 1 x RS-232, 1 x RS-232/422/485                                                 |  |  |  |  |

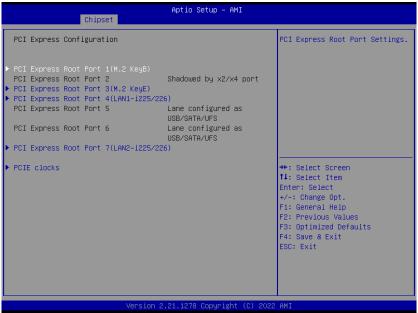

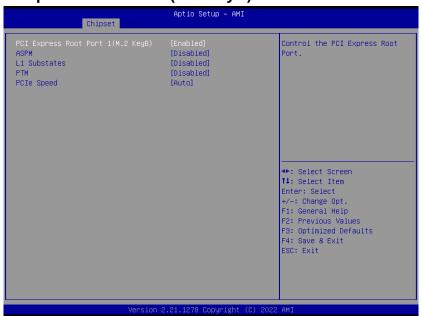

|                      | 1 x M.2 Type B 2242/2260 with (1 x PCI-e x2 via OEM BIOS request) or (1 x      |  |  |  |  |

|                      | PCI-e x1 + USB3.1 GEN 1)-Default or (1 x SATA III + USB3.1 GEN 1), USB2.0      |  |  |  |  |

|                      | Signal support SSD. (Default: SATA)                                            |  |  |  |  |

|                      | 1 x M.2 Type E 2230 support WiFi module, USB 2.0 Signal                        |  |  |  |  |

|                      | GPIO 4bit                                                                      |  |  |  |  |

|                      | DC in +12V                                                                     |  |  |  |  |

|                      | System                                                                         |  |  |  |  |

| CPU                  | Intel® Atom® x6000E Series and Intel® Pentium® and Celeron® J Series           |  |  |  |  |

| CPU                  | processors with CPU Bottom Mounted                                             |  |  |  |  |

| BIOS                 | AMI uEFI BIOS, 256Mbit SPI Flash ROM                                           |  |  |  |  |

| I/O Chip             | EC ITE IT5571 (IT5571VG-I for wide temp version)                               |  |  |  |  |

|                      | One 260-pin DDR4 2666MHz SO-DIMM socket, supports up to 32GB Max (Only         |  |  |  |  |

| System Memory        | Atom® x6000 Series Processors support IBECC)                                   |  |  |  |  |

| System Memory        | *Note: Due to mainboard design limitation, the mainboard is not recommend to   |  |  |  |  |

|                      | use DDR4 3200MHz SO-DIMM.                                                      |  |  |  |  |

| Watchdog Timer       | H/W Reset, 1sec. – 65535sec./min.1sec. or 1min. step                           |  |  |  |  |

| H/W Status Monitor   | CPU temperature monitoring                                                     |  |  |  |  |

| TI/VV Status WOTHLOT | Voltages monitoring                                                            |  |  |  |  |

|                      | Expansion Slot                                                                 |  |  |  |  |

|                      | 1 x M.2 Type B 2242/2260 with (1 x PCI-e x2 via OEM BIOS request) or (1 x      |  |  |  |  |

| M.2 Key B            | PCI-e x 1 + USB3.1 GEN1) or (1 x SATA III + USB3.1 GEN1), USB2.0 Signal,       |  |  |  |  |

| WILE NOY B           | support SSD.                                                                   |  |  |  |  |

|                      | 1 x M.2 Type E 2230 support WiFi module, USB 2.0 Signal                        |  |  |  |  |

|                      | Storage                                                                        |  |  |  |  |

| M.2                  | 1 x M.2 Type B 2242/2260 PCI-e or SATA SSD                                     |  |  |  |  |

|                      | Edge I/O                                                                       |  |  |  |  |

| LAN                  | 2 x Intel® I225/i226LM(I225/i226IT for wide temp version) 2.5 Gigabit Ethernet |  |  |  |  |

| USB 3.1 1 x Dual stack USB 3.1 GEN 2 connector                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DP                                                                                    | DP 1 x Dual stack DP(Upper DP, Lower DP++)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| DC Input                                                                              | 1 x DC Jack lockable connector type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Onboard I/O                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                                       | COM 1 : (JCOM1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| COM                                                                                   | 1 x 2 x 5 pin, pitch 1.27mm connector for RS-232/422/485                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| COM                                                                                   | COM 2 : (JCOM2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                                       | 1 x 2 x 5 pin, pitch 1.27mm connector for RS-232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| USB 2.0                                                                               | 1 x 2 x 6 pin, pitch 1.27mm connector for 4 USB 2.0 (JUSB1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| GPIO                                                                                  | 1 x 2 x 6 pin, pitch 1.25mm connector for GPIO: 4bits (JDIO1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Front Panel                                                                           | 1 x 2 x 5 pin, pitch 1.00mm connector for front panel (JFP1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| RTC Battery                                                                           | 1 x horizontal type battery connector (Battery cable 170mm length) (JBT1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| AT/ATX Selector                                                                       | 1 x 2 x 2 pin, pitch 1.27mm switch for AT/ATX mode (AT_CMOS1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| LVDS                                                                                  | CH7511B-BFI Single channel 18/24-bits LVDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| LVDS                                                                                  | 1 x 2 x 15 pin, pitch 1.00mm connector for LVDS (JLVDS1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| LCD Inverter                                                                          | PWM Mode (By Resistance) Backlight signal combined into LVDS connector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| BIOS SPI 1 x 2 x 6 pin, pitch 1.00mm connector for BIOS SPI (JESPI1,)/80 port         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| EC Debug/ eSPI 1 x 1 x 10 pin, pitch 1.00mm connector for EC+BIOS debug (JSPI_EC1,)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Activity Indicator                                                                    | By Activity Indicator LED (Boot LED, D23)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| LED                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                                       | Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Graphic Chipset                                                                       | Display  Intel® UHD Graphics for 10th Gen Intel® Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Graphic Chipset                                                                       | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Graphic Chipset                                                                       | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                                                                       | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF (CH7511B-BFI for wide temp version) eDP to LVDS)                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Graphic Chipset  Spec. & Resolution                                                   | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF  (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                                                       | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF  (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Spec. & Resolution                                                                    | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF  (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)  LVDS: 1366 x 768 Single channel 18/24-bits                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                       | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF  (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)  LVDS: 1366 x 768 Single channel 18/24-bits  Triple Display                                                                                                                                                                                                                                                                     |  |  |  |

| Spec. & Resolution  Multiple Display                                                  | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF  (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)  LVDS: 1366 x 768 Single channel 18/24-bits  Triple Display  Ethernet                                                                                                                                                                                                                                                           |  |  |  |

| Spec. & Resolution                                                                    | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF  (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)  LVDS: 1366 x 768 Single channel 18/24-bits  Triple Display  Ethernet  2 x Intel® I225/i226LM(I225/i226IT for wide temp version) 2.5 Gigabit Ethernet                                                                                                                                                                           |  |  |  |

| Spec. & Resolution  Multiple Display                                                  | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below: DP: 3840x2160(60Hz) LVDS: 1366 x 768 Single channel 18/24-bits  Triple Display  Ethernet  2 x Intel® I225/i226LM(I225/i226IT for wide temp version) 2.5 Gigabit Ethernet 10/100/1000 Base-Tx GbE compatible                                                                                                                                            |  |  |  |

| Spec. & Resolution  Multiple Display  LAN Chipset  LAN Spec.                          | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF  (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)  LVDS: 1366 x 768 Single channel 18/24-bits  Triple Display  Ethernet  2 x Intel® I225/i226LM(I225/i226IT for wide temp version) 2.5 Gigabit Ethernet  10/100/1000 Base-Tx GbE compatible  2.5 Gigabit Ethernet                                                                                                                 |  |  |  |

| Spec. & Resolution  Multiple Display  LAN Chipset  LAN Spec.                          | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF  (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)  LVDS: 1366 x 768 Single channel 18/24-bits  Triple Display  Ethernet  2 x Intel® I225/i226LM(I225/i226IT for wide temp version) 2.5 Gigabit Ethernet  10/100/1000 Base-Tx GbE compatible  2.5 Gigabit Ethernet  Mechanical & Environmental Specification                                                                       |  |  |  |

| Spec. & Resolution  Multiple Display  LAN Chipset  LAN Spec.                          | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF  (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)  LVDS: 1366 x 768 Single channel 18/24-bits  Triple Display  Ethernet  2 x Intel® I225/i226LM(I225/i226IT for wide temp version) 2.5 Gigabit Ethernet  10/100/1000 Base-Tx GbE compatible  2.5 Gigabit Ethernet  Mechanical & Environmental Specification  DC in +12V                                                           |  |  |  |

| Spec. & Resolution  Multiple Display  LAN Chipset  LAN Spec.                          | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)  LVDS: 1366 x 768 Single channel 18/24-bits  Triple Display  Ethernet  2 x Intel® I225/i226LM(I225/i226IT for wide temp version) 2.5 Gigabit Ethernet 10/100/1000 Base-Tx GbE compatible 2.5 Gigabit Ethernet  Mechanical & Environmental Specification  DC in +12V  Single power ATX Support S0, S3, S4, S5                     |  |  |  |

| Spec. & Resolution  Multiple Display  LAN Chipset  LAN Spec.  Power Requirement  ACPI | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)  LVDS: 1366 x 768 Single channel 18/24-bits  Triple Display  Ethernet  2 x Intel® I225/i226LM(I225/i226IT for wide temp version) 2.5 Gigabit Ethernet 10/100/1000 Base-Tx GbE compatible 2.5 Gigabit Ethernet  Mechanical & Environmental Specification  DC in +12V  Single power ATX Support S0, S3, S4, S5  ACPI 5.1 Compliant |  |  |  |

| Spec. & Resolution  Multiple Display  LAN Chipset  LAN Spec.  Power Requirement       | Intel® UHD Graphics for 10th Gen Intel® Processors  One dual stack DP(Upper DP, Lower DP++): 4096 x 2160@60 Hz  LVDS: 1366 x 768 Single channel 18/24-bits LVDS (Chrontel CH7511B-BF (CH7511B-BFI for wide temp version) eDP to LVDS)  Note: This is Intel resolution. DQV actual test resolution as below:  DP: 3840x2160(60Hz)  LVDS: 1366 x 768 Single channel 18/24-bits  Triple Display  Ethernet  2 x Intel® I225/i226LM(I225/i226IT for wide temp version) 2.5 Gigabit Ethernet 10/100/1000 Base-Tx GbE compatible 2.5 Gigabit Ethernet  Mechanical & Environmental Specification  DC in +12V  Single power ATX Support S0, S3, S4, S5                     |  |  |  |

#### User's Manual

|                    | 1                                                                                   | User's | Manual |

|--------------------|-------------------------------------------------------------------------------------|--------|--------|

|                    | -20~60°C (-4~140°F) Elkhart Lake Atom Series CPU SKU                                |        |        |

|                    | w/HDD/SSD, ambient with 0.5 m/s Air flow                                            |        |        |

| Storage Temp.      | -40~ +75°C                                                                          |        |        |

| Operating Humidity | 40°C @ 95% Relative Humidity, Non-condensing                                        |        |        |

| Size (L x W)       | 2.5" SBC Form Factor                                                                |        |        |

| OIZC (L X VV)      | 3.937" x 2.834" (100mm x 72mm)                                                      |        |        |

| Weight             | 0.40kg                                                                              |        |        |

|                    | Package Vibration Test                                                              |        |        |

|                    | Reference IEC60068-2-64 Testing procedures                                          |        |        |

|                    | Test Fh: Vibration broadband random Test                                            |        |        |

|                    | PSD: 0.026G <sup>2</sup> /Hz, 2.16 Grms                                             |        |        |

|                    | Non-operation mode                                                                  |        |        |

|                    | Test Frequency: 5-500Hz                                                             |        |        |

|                    | Test Axis: X,Y and Z axis                                                           |        |        |

|                    | 30 min. per each axis                                                               |        |        |

|                    | IEC 60068-2-64 Test:Fh                                                              |        |        |

|                    |                                                                                     |        |        |

|                    | Random Vibration Operation                                                          |        |        |

|                    | Reference IEC60068-2-64 Testing procedures                                          |        |        |

|                    | Test Fh : Vibration broadband random Test                                           |        |        |

|                    | PSD: 0.00454G <sup>2</sup> /Hz, 1.5 Grms                                            |        |        |

| Vibration Test     | Operation mode                                                                      |        |        |

| Vibration rest     | Test Frequency : 5-500Hz                                                            |        |        |

|                    | Test Axis : X,Y and Z axis                                                          |        |        |

|                    | 30 minutes per each axis                                                            |        |        |

|                    | IEC 60068-2-64 Test:Fh                                                              |        |        |

|                    | Dandom Vibration Non Operation                                                      |        |        |

|                    | Random Vibration Non Operation                                                      |        |        |

|                    | Reference IEC60068-2-64 Testing procedures Test Fh: Vibration broadband random Test |        |        |

|                    |                                                                                     |        |        |

|                    | PSD: 0.01818G <sup>2</sup> /Hz, 3.0 Grms  Non Operation mode                        |        |        |

|                    | Test Frequency : 5-500Hz                                                            |        |        |

|                    | Test Axis: X,Y and Z axis                                                           |        |        |

|                    |                                                                                     |        |        |

|                    | 30 minutes per each axis                                                            |        |        |

|                    | IEC 60068-2-64 Test:Fh                                                              |        |        |

|                    | Packing Drop                                                                        |        |        |

| Drop Test          | Reference ISTA 2A, Method : IEC-60068-2-32 Test: Ed                                 |        |        |

|                    | Drop Test                                                                           |        |        |

|                    | 1                                                                                   |        |        |

|                | 1 One corner , three edges, six faces |  |  |

|----------------|---------------------------------------|--|--|

|                | 2 ISTA 2A, IEC-60068-2-32 Test:Ed     |  |  |

| OS Information | Win10 64bit, Linux                    |  |  |

**Note:** Specifications are subject to change without notice.

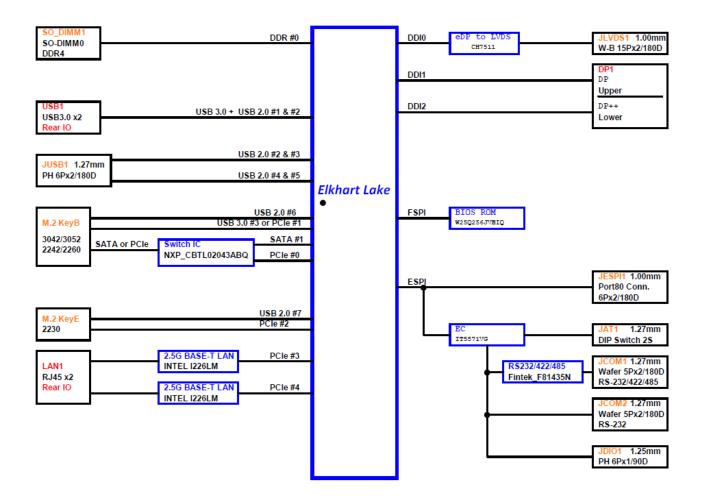

# 1.6 Architecture Overview—Block Diagram

The following block diagram shows the architecture and main components of EPX-EHLP.

# 2. HardwareConfiguration

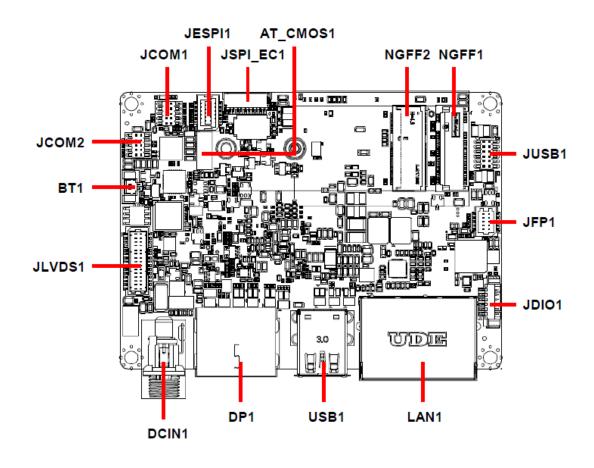

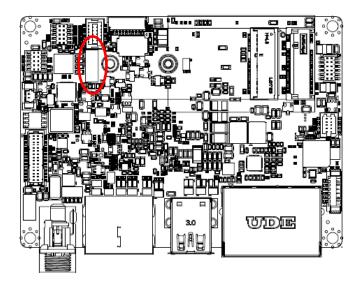

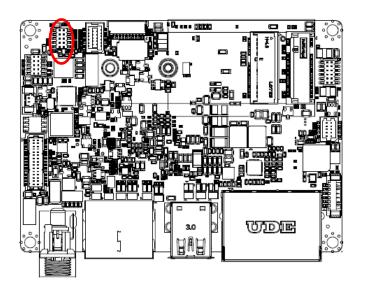

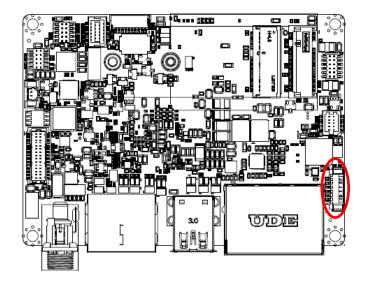

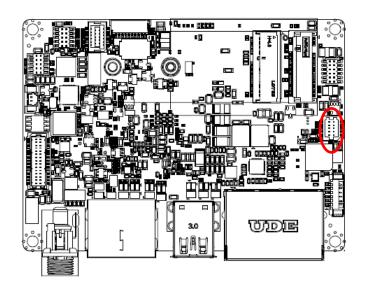

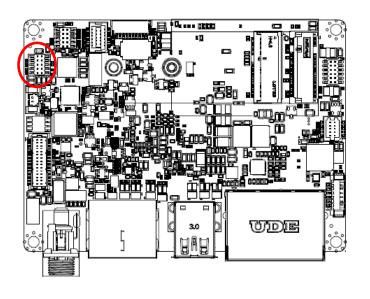

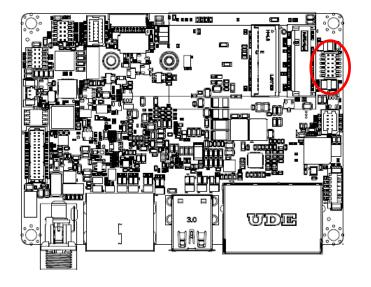

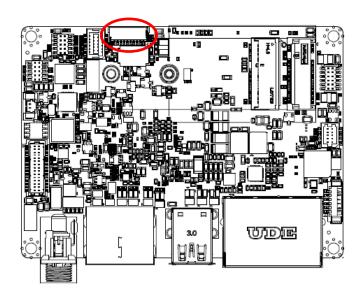

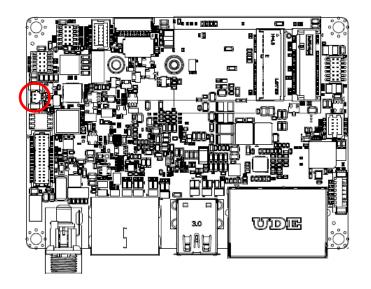

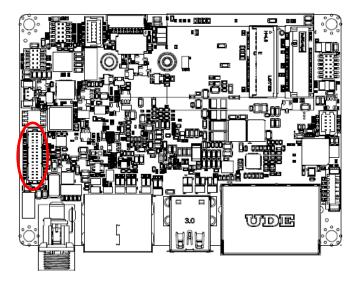

# 2.1 Product Overview

# 2.2 Jumper and Connector List

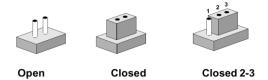

You can configure your board to match the needs of your application by setting jumpers. A jumper is the simplest kind of electric switch.

It consists of two metal pins and a small metal clip (often protected by a plastic cover) that slides over the pins to connect them. To "close" a jumper you connect the pins with the clip. To "open" a jumper you remove the clip. Sometimes a jumper will have three pins, labeled 1, 2, and 3. In this case, you would connect either two pins.

The jumper settings are schematically depicted in this manual as follows:

A pair of needle-nose pliers may be helpful when working with jumpers.

Connectors on the board are linked to external devices such as hard disk drives, a keyboard, or floppy drives. In addition, the board has a number of jumpers that allow you to configure your system to suit your application.

If you have any doubts about the best hardware configuration for your application, contact your local distributor or sales representative before you make any changes.

The following tables list the function of each of the board's jumpers and connectors.

| Connectors |                                 |                             |

|------------|---------------------------------|-----------------------------|

| Label      | Function                        | Note                        |

| AT_CMOS1   | AT/ATX mode selector            |                             |

| BT1        | Battery connector               | 2 x 1 wafer, pitch 1.25 mm  |

| JFP1       | Miscellaneous setting connector | 5 x 2 wafer, pitch 1.00 mm  |

| DCIN1      | DC Power-in connector           |                             |

| DP1        | DP connector                    |                             |

| LAN1       | RJ-45 Ethernet connector        |                             |

| JCOM1/2    | Serial port 1/2 connector       | 5 x 2 header, pitch 1.27 mm |

| JLVDS1     | LVDS connector                  | 15 x 2 wafer, pitch 1.00 mm |

| JDIO1      | General purpose I/O connector   | 6 x 1 wafer, pitch 1.25 mm  |

| JSPI_EC1   | JSPI_EC connector               | 10 x 1 wafer, pitch 1.00 mm |

| JESPI1     | JESPI connector                 | 6 x 2 wafer, pitch 1.00 mm  |

| JUSB1    | USB connector    | 6 x 2 header, pitch 1.27 mm |

|----------|------------------|-----------------------------|

| USB1     | USB3.0 connector |                             |

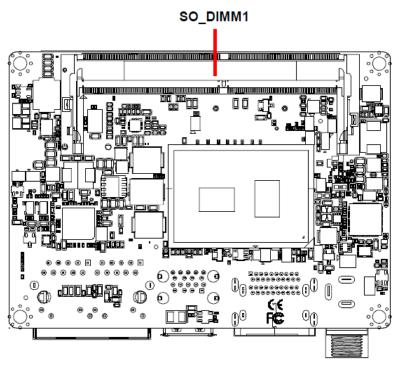

| SO_DIMM1 | 260-pin DDR4     |                             |

| NGFF1    | M.2 B key slot   |                             |

| NGFF2    | M.2 E Key slot   |                             |

Note: Please note interferance may occcur if customer may use both Key E & Key B modules together.

It is recommend to use standard 1.5mm thickness for Key E module. Bottom of Key B module height shall not be thicker than 1.1mm.

# 2.3 Setting Jumpers & Connectors

# 2.3.1 AT/ATX mode selector (AT\_CMOS1)

\*Default

AT/ATX mode

AT mode\* ATX mode

# 2.3.2 JESPI connector (JESPI 1)

| П | 1  |

|---|----|

| 0 |    |

| _ |    |

| _ |    |

|   |    |

| _ | 11 |

| Signal      | PIN | PIN | Signal       |

|-------------|-----|-----|--------------|

| CN_ESPI_IO0 | 2   | 1   | +3.3_ ESPI   |

| CN_ESPI_IO1 | 4   | 3   | PLT_RST_BUT# |

| CN_ESPI_IO2 | 6   | 5   | ESPI_CS#0    |

| CN_ESPI_IO3 | 8   | 7   | CN_ESPI_CLK  |

| NC          | 10  | 9   | GND          |

| ESPI_RST    | 12  | 11  | ESPI_ALERT#0 |

#### 2.3.3 **General purpose I/O connector (JDIO1)**

| Signal | PIN |

|--------|-----|

| GND    | 6   |

| EC_DI1 | 5   |

| EC_DI0 | 4   |

| EC_DO1 | 3   |

| EC_DO0 | 2   |

| +3.3V  | 1   |

#### **Miscellaneous setting connector (JFP1)** 2.3.4

| Signal         | PIN | PIN | Signal      |

|----------------|-----|-----|-------------|

| PWR_LED+       | 1   | 2   | HDD_LED+    |

| PWR_LED#       | 3   | 4   | HDD_LED#    |

| PWR_BTN_IN_EC# | 5   | 6   | PMC_RSTBTN# |

| GND            | 7   | 8   | GND         |

| NC             | 9   | 10  | NC          |

# 2.3.5 Serial port 1 connector (JCOM1)

| 1 |   | 0 |

|---|---|---|

|   |   | 0 |

|   | _ | _ |

|   |   | 0 |

| 9 | _ | 0 |

| Signal         | PIN | PIN | Signal         |

|----------------|-----|-----|----------------|

| COM_DCD#_TXN_1 | 1   | 2   | COM_RXD#_TXP_1 |

| COM_TXD_RXP_1  | 3   | 4   | COM_DTR#_RXN_1 |

| GND            | 5   | 6   | COM_DSR#_1     |

| COM_RTS#_1     | 7   | 8   | COM_CTS#_1     |

| COM_RI#_1      | 9   | 10  | NC             |

# 2.3.6 Serial port 2 connector (JCOM2)

| Signal      | PIN | PIN | Signal     |

|-------------|-----|-----|------------|

| COM_DCD# _2 | 1   | 2   | COM_RXD#_2 |

| COM_TXD_2   | 3   | 4   | COM_DTR#_2 |

| GND         | 5   | 6   | COM_DSR#_2 |

| COM_RTS#_2  | 7   | 8   | COM_CTS#_2 |

| COM_RI#_2   | 9   | 10  | NC         |

#### 2.3.7 **USB** connector (JUSB 1)

| 1  | П | П |

|----|---|---|

|    | 0 | 0 |

|    | 0 | 0 |

|    | 0 | 0 |

|    | 0 | 0 |

| 11 | 0 | 0 |

| Signal    | PIN | PIN | Signal    |

|-----------|-----|-----|-----------|

| GND       | 1   | 2   | +5A_USB23 |

| USB_R_DN2 | 3   | 4   | USB_R_DN3 |

| USB_R_DN2 | 5   | 6   | USB_R_DN3 |

| USB_R_DN4 | 7   | 8   | USB_R_DN5 |

| USB_R_DN4 | 9   | 10  | USB_R_DN5 |

| GND       | 11  | 12  | +5A_USB45 |

#### SPI header (JSPI\_EC1) 2.3.8

| Signal       | PIN |

|--------------|-----|

| EC_SMDAT_DBG | 1   |

| EC_SMCLK_DBG | 2   |

| NC           | 3   |

| SPI_HOLD#    | 4   |

| SPI_MOSI     | 5   |

| SPI_MISO     | 6   |

| SPI_CLK      | 7   |

| SPI_CS#0     | 8   |

| GND          | 9   |

| +V3.3A_SPI   | 10  |

# 2.3.9 Battery connector (BT1)

| Signal  | PIN |

|---------|-----|

| +3.3VSB | 1   |

| GND     | 2   |

# 2.3.10 LVDS connector (JLVDS1)

| Signal       | PIN | PIN | Signal       |

|--------------|-----|-----|--------------|

| +V3.3_LVDS   | 1   | 2   | +V5_LVDS     |

| GND          | 3   | 4   | GND          |

| GND          | 5   | 6   | GND          |

| GND          | 7   | 8   | GND          |

| LVDS_DATA1_P | 9   | 10  | LVDS_DATA0_P |

| LVDS_DATA1_N | 11  | 12  | LVDS_DATA0_N |

| GND          | 13  | 14  | GND          |

| LVDS_DATA3_P | 15  | 16  | LVDS_DATA2_P |

| LVDS_DATA3_N | 17  | 18  | LVDS_DATA2_N |

| GND          | 19  | 20  | GND          |

| LVDS_BKLTEN  | 21  | 22  | LVDS_CLK1_P  |

| VBRIGHT      | 23  | 24  | LVDS_CLK1_N  |

| GND          | 25  | 26  | GND          |

| +12V         | 27  | 28  | +5V          |

| GND          | 29  | 30  | GND          |

#### Note:

Mainboard Connector: Aces 50238-03071-003 or

Equivalent

User Side Connector: WELL-LIN 1010-H-2X15P or

Equivalent

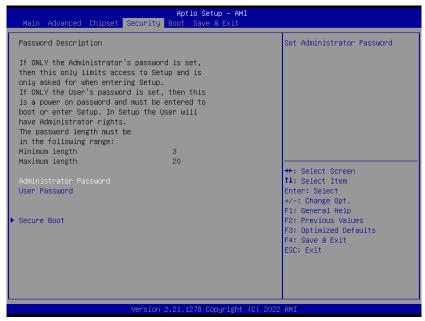

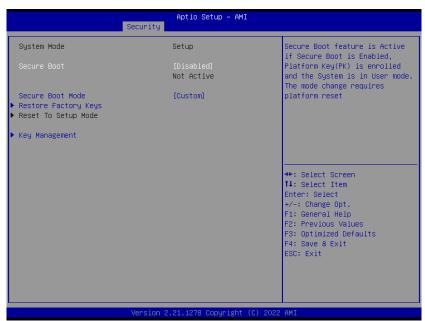

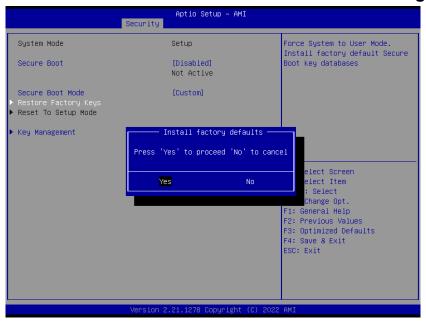

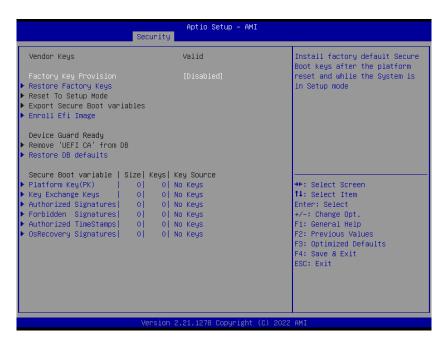

# 3.BIOS Setup

#### 3.1 Introduction

The BIOS setup program allows users to modify the basic system configuration. In this following chapter will describe how to access the BIOS setup program and the configuration options that may be changed.

# 3.2 Starting Setup

AMI BIOS™ is immediately activated when you first power on the computer. The BIOS reads the system information contained in the NVRAM and begins the process of checking out the system and configuring it. When it finishes, the BIOS will seek an operating system on one of the disks and then launch and turn control over to the operating system.

While the BIOS is in control, the Setup program can be activated in one of two ways: By pressing <DEL> or <ESC> immediately after switching the system on, or By pressing the <DEL> or <ESC> key when the following message appears briefly at the left-top of the screen during the POST (Power On Self Test).

#### Press <DEL> or <ESC> to enter SETUP

If the message disappears before you respond and you still wish to enter Setup, restart the system to try again by turning it OFF then ON or pressing the "RESET" button on the system case. You may also restart by simultaneously pressing <Ctrl>, <Alt>, and <Delete> keys.

# 3.3 Using Setup

In general, you use the arrow keys to highlight items, press <Enter> to select, use the PageUp and PageDown keys to change entries, press <F1> for help and press <Esc> to quit. The following table provides more detail about how to navigate in the Setup program using the keyboard.

| Button                                       | Description                |

|----------------------------------------------|----------------------------|

| $\uparrow \downarrow \rightarrow \leftarrow$ | Move                       |

| Enter                                        | Select                     |

| +/-                                          | Value                      |

| ESC                                          | Exit                       |

| F1 key                                       | General Help               |

| F2 key                                       | Previous Values            |

| F3 key                                       | Optimized Defaults         |

| F4 key                                       | Save & Exit Setup          |

| <k></k>                                      | Scroll help area upwards   |

| <m></m>                                      | Scroll help area downwards |

#### Navigating Through The Menu Bar

Use the left and right arrow keys to choose the menu you want to be in.

**Note:** Some of the navigation keys differ from one screen to another.

#### To Display a Sub Menu

Use the arrow keys to move the cursor to the sub menu you want. Then press <Enter>. A ">" pointer marks all sub menus.

#### 3.4 Getting Help

Press F1 to pop up a small help window that describes the appropriate keys to use and the possible selections for the highlighted item. To exit the Help Window press <Esc> or <Enter> key.

#### 3.5 In Case of Problems

If, after making and saving system changes with Setup, you discover that your computer no longer is able to boot, the AMI BIOS supports an override to the NVRAM settings which resets your system to its defaults.

The best advice is to only alter settings which you thoroughly understand. To this end, we strongly recommend that you avoid making any changes to the chipset defaults. These defaults have been carefully chosen by both BIOS Vendor and your systems manufacturer to provide the absolute maximum performance and reliability. Even a seemingly small change to the chipset setup has the potential for causing you to use the override.

# 3.6 BIOS setup

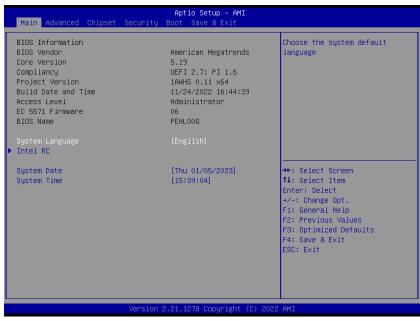

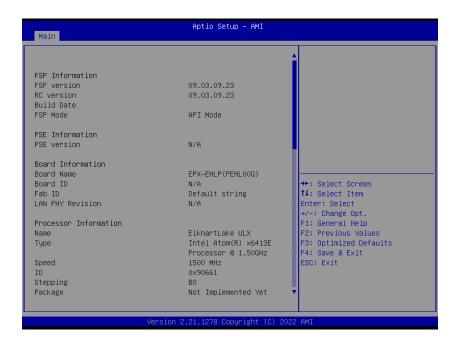

Once you enter the Aptio Setup Utility, the Main Menu will appear on the screen. The Main Menu allows you to select from several setup functions and exit choices. Use the arrow keys to select among the items and press <Enter> to accept and enter the sub-menu.

#### 3.6.1 Main Menu

This section allows you to record some basic hardware configurations in your computer and set the system clock.

#### 3.6.1.1 System Language

This option allows choosing the system default language.

#### **3.6.1.2** System Date

Use the system date option to set the system date. Manually enter the day, month and year.

#### **3.6.1.3** System Time

Use the system time option to set the system time. Manually enter the hours, minutes and seconds.

Note: The BIOS setup screens shown in this chapter are for reference purposes only, and may not exactly match what you see on your screen.

Visit the Avalue website (www.avalue.com.tw) to download the latest product and BIOS information.

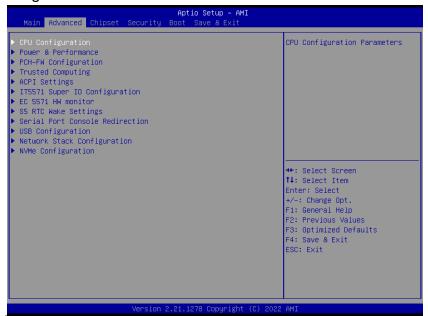

#### 3.6.2 Advanced Menu

This section allows you to configure your CPU and other system devices for basic operation through the following sub-menus.

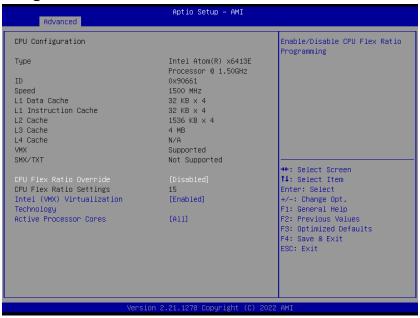

# 3.6.2.1 CPU Configuration

| Item                                     | Options                                  | Description                                                                                             |

|------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------|

| CPU Flex Ratio Override                  | Disabled <b>[Default]</b> ,<br>Enabled   | Enables/Disables CPU Flex Ratio Programming                                                             |

| Intel (VMX) Virtualization<br>Technology | Disabled,<br>Enabled[ <b>Default]</b>    | When enabled, a VMM can utilize the additional hardware capabilities provided by Vanderpool Technology. |

| Active Processor Cores                   | All <b>[Default]</b><br>/1/2/3/4/5/6/7/8 | Number of cores to enable in each processor package.                                                    |

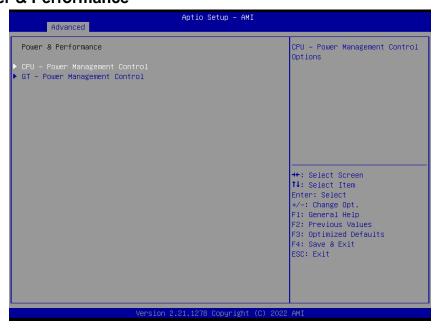

#### 3.6.2.2 Power & Performance

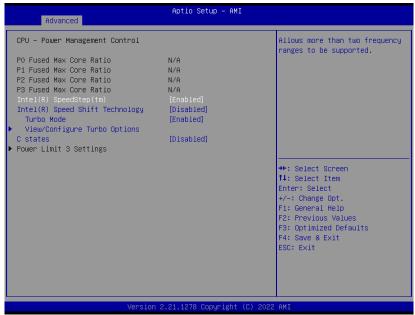

#### 3.6.2.2.1 CPU - Power Management Control

| Item                               | Options                                | Description                                                                                                                                   |

|------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Intel(R) SpeedStep(tm)             | Disabled<br>Enabled <b>[Default]</b> , | Allows more than two frequency ranges to be supported.                                                                                        |

| Intel(R) Speed Shift<br>Technology | Disabled <b>[Default]</b><br>Enabled,  | Enable/Disable Intel(R) Speed Shift Technology support. Enabling will expose the CPPC v2 interface to allow for hardware controlled P-states. |

| Turbo Mode                         | Disabled<br>Enabled <b>[Default]</b> , | Enable/Disable processor Turbo Mode (requires EMTTM enabled too). Auto means enabled.                                                         |

| C states                           | Disabled <b>[Default]</b><br>Enabled,  | Enable/Disable CPU Power Management. Allows CPU to go to C states when it's not 100% utilized.                                                |

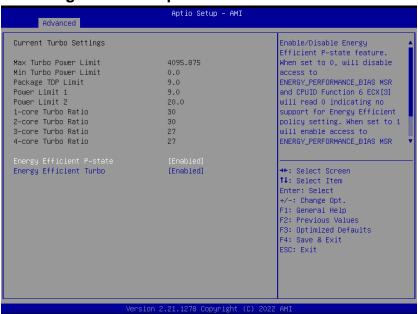

#### **View/Configure Turbo Options** 3.6.2.2.1.1

| Item                        | Options                                | Description                                                                                                                                                                                                                                                                                    |

|-----------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Energy Efficient<br>P-state | Disabled<br>Enabled <b>[Default]</b> , | Enable/Disable Energy Efficient P-state feature. When set to 0, will disable access to ENERGY_PERFORMANCE_BIAS MSR and CPUID Function 6 ECX[3] will read 0 indicating no support for Energy Efficient policy setting. When set to 1 will enable access to ENERGY_PERFORMANCE_BIAS MSR 1B0h and |

| Energy Efficient Turbo      | Disabled <b>[Default]</b><br>Enabled,  | Enable/Disable Energy Efficient Turbo Feature. This feature will opportunistically lower the turbo frequency to increase efficiency. Recommended only to disable in overclocking situations where turbo frequency must remain constant. Otherwise, leave enabled.                              |

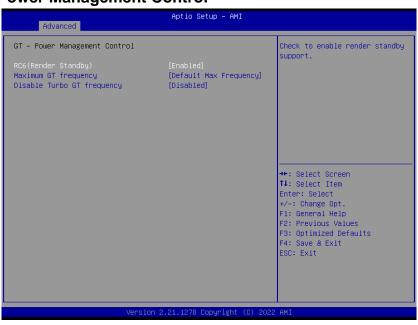

# 3.6.2.2.2 GT - Power Management Control

| Item                       | Options                                                                                                                                                                                                                           | Description                                                                |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| RC6(Render<br>Standby)     | Disabled<br>Enabled <b>[Default]</b> ,                                                                                                                                                                                            | Cheak to enable render standby support.                                    |

| Maximum GT<br>frequency    | Default Max Frequency[ <b>Default</b> ],<br>100Mhz/150Mhz/200Mhz/250Mhz/300Mhz/<br>350Mhz/400Mhz/450Mhz/500Mhz/550Mhz/<br>600Mhz/650Mhz/700Mhz/750Mhz/800Mhz/<br>850Mhz/900Mhz/950Mhz/1000Mhz/<br>1050Mhz/1100Mhz/1150Mhz/1200Mhz | Auto Updated                                                               |

| Disable Turbo GT frequency | Disabled <b>[Default]</b> ,<br>Enabled                                                                                                                                                                                            | Enabled: Disable Turbo GT frequency. Disabled: GT frequency is not limited |

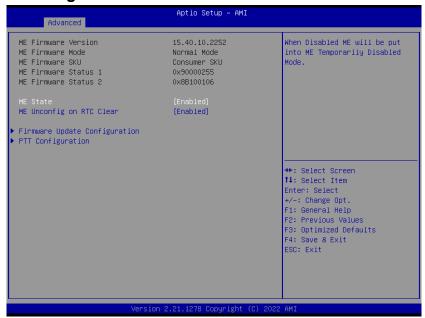

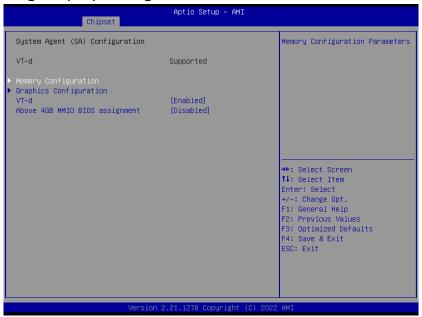

#### 3.6.2.3 PCH-FW Configuration

| Item                     | Options                                | Description                                                     |

|--------------------------|----------------------------------------|-----------------------------------------------------------------|

| ME State                 | Disabled<br>Enabled <b>[Default]</b> , | When Disabled ME will be put into ME Temporarily Disabled Mode. |

| ME Unconfig on RTC Clear | Disabled<br>Enabled <b>[Default]</b> , | When Disabled ME will not be unconfigured on RTC Clear          |

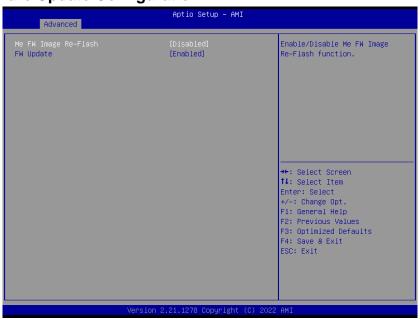

# 3.6.2.3.1 Firmware Update Configuration

| Item                 | Options                                | Description                                   |

|----------------------|----------------------------------------|-----------------------------------------------|

| Me FW Image Re-Flash | Disabled <b>[Default]</b> ,<br>Enabled | Enable/Disable Me FW Image Re-Flash function. |

| FW Update            | Disabled<br>Enabled <b>[Default]</b> , | Enable/Disable ME FW Update function.         |

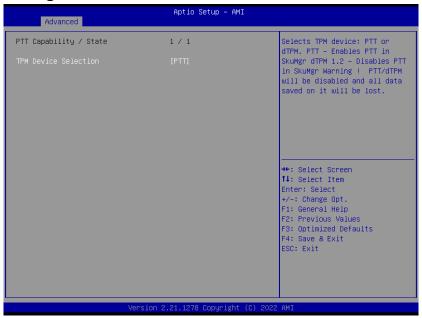

# 3.6.2.3.2 PTT Configuration

| Item                 | Options                        | Description                                                                                                                                                              |

|----------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPM Device Selection | dTPM<br>PTT <b>[Default]</b> , | Selects TPM device: PTT or dTPM. PTT - Enables PTT in SkuMgr dTPM 1.2 - Disables PTT in SkuMgr Warning! PTT/dTPM will be disabled and all data saved on it will be lost. |

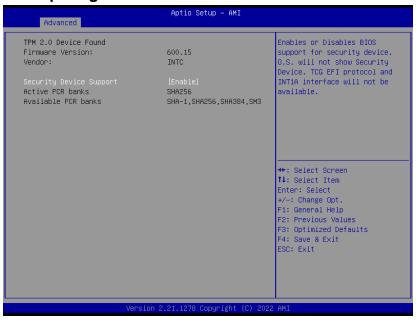

#### 3.6.2.4 Trusted Computing

| Item                    | Options                            | Description                                                                                                                                            |

|-------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security Device Support | Disable<br>Enable <b>[Default]</b> | Enables or Disables BIOS support for security devices. O.S. will not show Security Device. TCG EFI protocol and INT1A interface will not be available. |

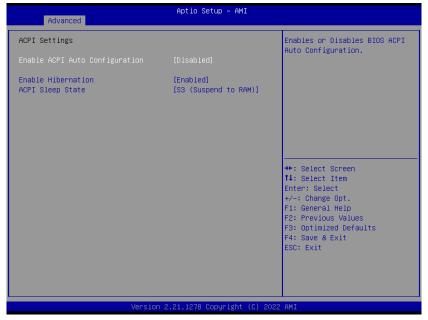

# 3.6.2.5 ACPI Settings

| Item                              | Options                                               | Description                                                                                                                        |

|-----------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Enable ACPI Auto<br>Configuration | Disabled <b>[Default]</b><br>Enabled                  | Enables or Disables BIOS ACPI Auto Configuration                                                                                   |

| Enable Hibernation                | Disabled<br>Enabled <b>[Default]</b>                  | Enables or Disables System ability to Hibernate (OS/S4 Sleep State). This option may be not effective with some operating systems. |

| ACPI Sleep State                  | Suspend Disabled,<br>S3 (Suspend to RAM)<br>[Default] | Select the highest ACPI sleep state the system will enter when the SUSPEND button is pressed.                                      |

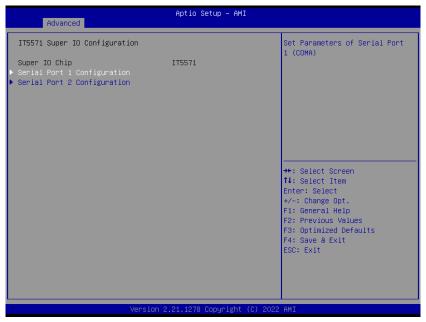

#### 3.6.2.6 IT5571 Super IO Configuration

You can use this item to set up or change the IT5571 Super IO configuration for serial ports. Please refer to 3.6.2.6.1 for more information.

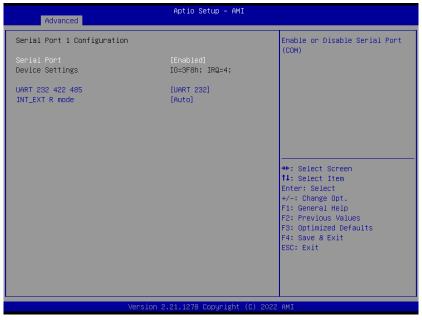

#### 3.6.2.6.1 Serial Port 1 Configuration

| Item             | Option                                                                | Description                                         |

|------------------|-----------------------------------------------------------------------|-----------------------------------------------------|

| Serial Port      | Disabled<br>Enabled[ <b>Default]</b>                                  | Enable or Disable Serial Port (COM)                 |

| UART 232 422 485 | UART 232 <b>[Default]</b><br>UART 422<br>UART 485                     | Change the Serial Port as RS232/422/485             |

| INT_EXT R mode   | Auto <b>[Default]</b><br>Non INT+EXT R<br>EXT R<br>INT R<br>INT+EXT R | Enable switches for internal and external resistors |

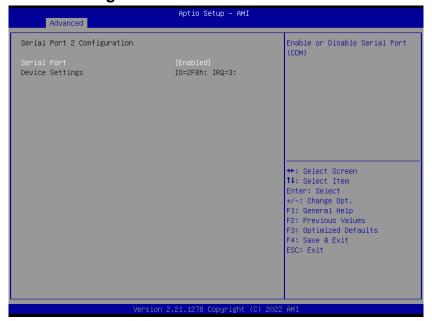

# 3.6.2.6.2 Serial Port 2 Configuration

| Item        | Option                               | Description                         |

|-------------|--------------------------------------|-------------------------------------|

| Serial Port | Disabled<br>Enabled[ <b>Default]</b> | Enable or Disable Serial Port (COM) |

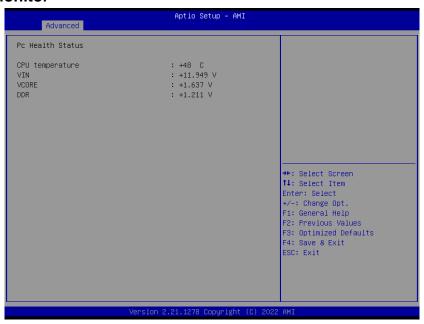

#### 3.6.2.7 H/W Monitor

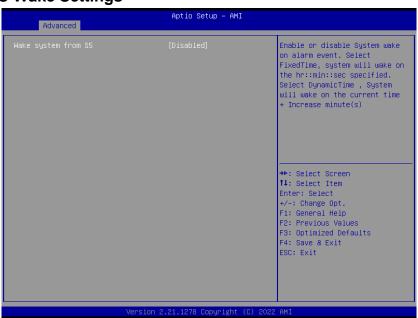

#### 3.6.2.8 S5 RTC Wake Settings

| Item                | Options                                             | Description                                                                                                                                                                                      |

|---------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wake system from S5 | Disabled <b>[Default]</b> , Fixed Time Dynamic Time | Enable or disable System wake on alarm event.  Select FixedTime, system will wake on the hr::min::sec specified. Select Dynamic Time, System will wake on the current time + Increase minute(s). |

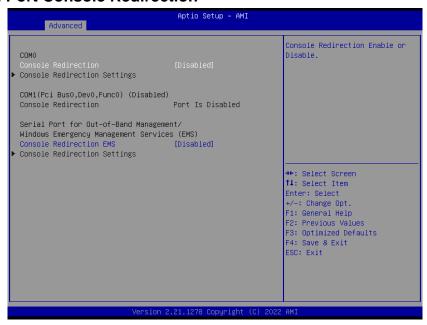

#### 3.6.2.9 Serial Port Console Redirection

| Item                | Options                                | Description                            |

|---------------------|----------------------------------------|----------------------------------------|

| Console Redirection | Disabled <b>[Default]</b> ,<br>Enabled | Console Redirection Enable or Disable. |

#### 3.6.2.10 USB Configuration

The USB Configuration menu helps read USB information and configures USB settings.

| Item               | Options                                      | Description                                                                                                                                                                 |

|--------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Legacy USB Support | Enabled <b>[Default]</b><br>Disabled<br>Auto | Enables Legacy USB support. AUTO option disables legacy support if no USB devices are connected.  DISABLE option will keep USB devices available only for EFI applications. |

#### User's Manual

|                                    |                                                          | Ţ                                                                                                                                                                                                          |

|------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|