# EHL9A2

COM Express Mini Module User's Manual

## Copyright

This publication contains information that is protected by copyright. No part of it may be reproduced in any form or by any means or used to make any transformation/adaptation without the prior written permission from the copyright holders.

This publication is provided for informational purposes only. The manufacturer makes no representations or warranties with respect to the contents or use of this manual and specifically disclaims any express or implied warranties of merchantability or fitness for any particular purpose. The user will assume the entire risk of the use or the results of the use of this document. Further, the manufacturer reserves the right to revise this publication and make changes to its contents at any time, without obligation to notify any person or entity of such revisions or changes.

Changes after the publication's first release will be based on the product's revision. The website will always provide the most updated information.

© 2023. All Rights Reserved.

## **Trademarks**

Product names or trademarks appearing in this manual are for identification purpose only and are the properties of the respective owners.

## **COM Express Specification Reference**

PICMG® COM Express® Module Base Specification. http://www.picmg.org/

## FCC and DOC Statement on Class B

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and the receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- · Consult the dealer or an experienced radio TV technician for help.

## **Notice:**

- The changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

- · Shielded interface cables must be used in order to comply with the emission limits.

## **Table of Contents**

| Chapter 1 - Introduction                                                                                        |          |

|-----------------------------------------------------------------------------------------------------------------|----------|

| Specification                                                                                                   |          |

| Chapter 2 - Concept                                                                                             | 9        |

| COM Express Module Standards                                                                                    | 9        |

| Chapter 3 - Hardware Installation                                                                               | 10       |

| Board Layout                                                                                                    |          |

| System Memory                                                                                                   | 10       |

| Connector                                                                                                       |          |

| COM Express Connector                                                                                           |          |

| System Memory                                                                                                   | 11<br>13 |

| COM Express Connector Signal Description                                                                        | 14       |

| COM Express Connector Signal Description                                                                        | 15       |

| COM Express Connector Signal Description                                                                        | 16<br>17 |

| COM Express Connector Signal Description                                                                        | 18       |

| COM Express Connector Signal Description                                                                        | 19       |

| COM Express Connector Signal Description                                                                        | 20       |

| COM Express Pin Assignments                                                                                     | 21       |

| Pin List for Pin-Out Type 10                                                                                    |          |

| Module Feature Fill Order                                                                                       |          |

| Feature Fill Order                                                                                              | 24       |

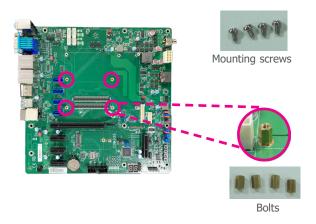

| Cooling Option                                                                                                  | 25       |

| Heat Sink                                                                                                       | 25       |

| Installing EHL9A2 onto a Carrier Board                                                                          | 25       |

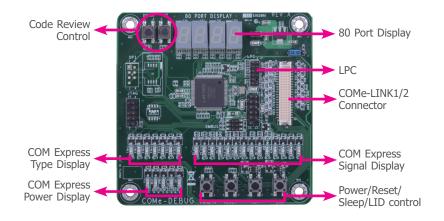

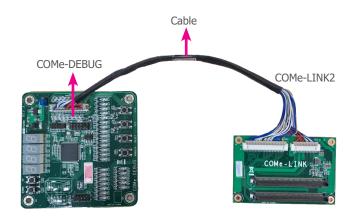

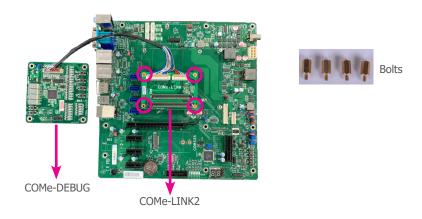

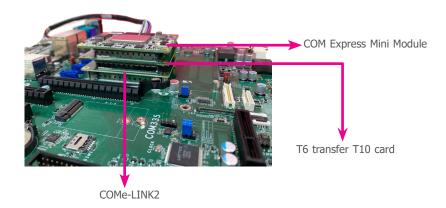

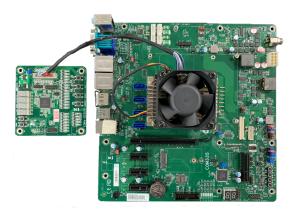

| Installing the COM Express Debug Card                                                                           | 26       |

| COMe-DEBUG                                                                                                      | 27       |

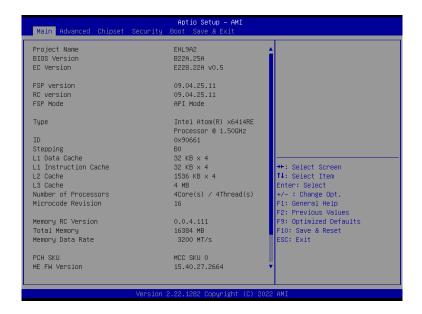

| Chapter 4 - BIOS Setup                                                                                          |          |

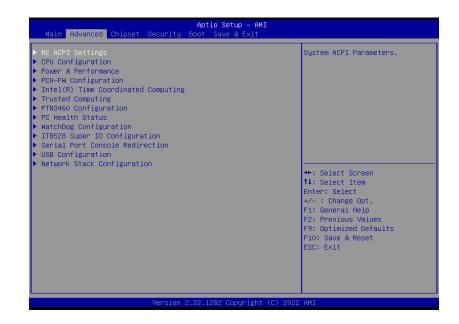

| Main<br>Advanced                                                                                                |          |

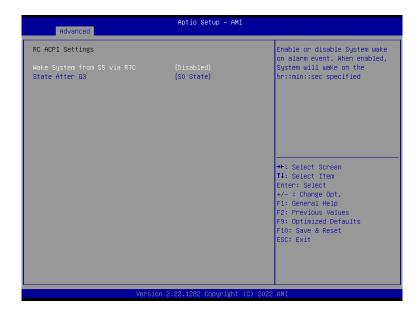

| RC ACPI Configuration                                                                                           |          |

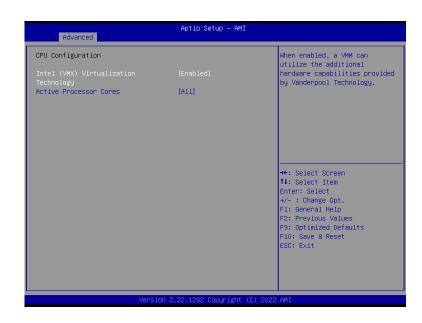

| CPU Configuration                                                                                               |          |

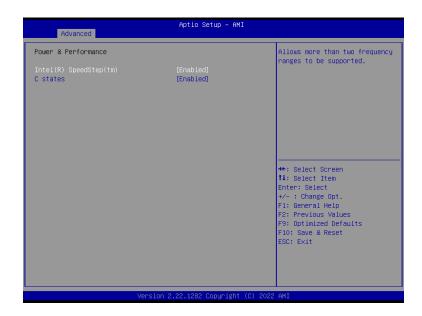

| Power & Performance                                                                                             | 32       |

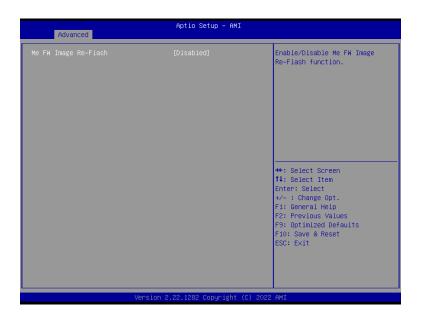

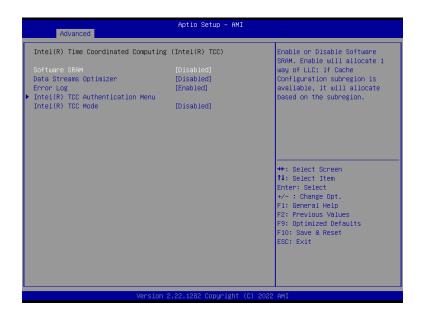

| PCH-FW Configuration<br>Intel(R) Time Coordinated Computing                                                     | 32       |

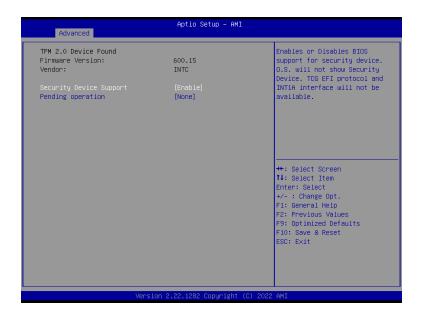

| Trusted Computing                                                                                               | 34       |

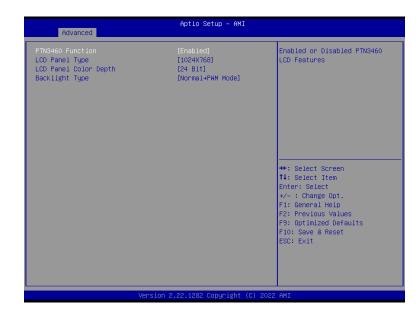

| PTN3460 Configuration                                                                                           | 34       |

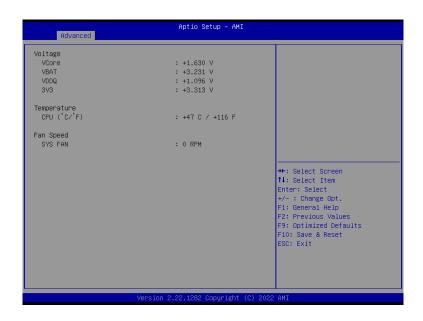

| PC Health Status                                                                                                |          |

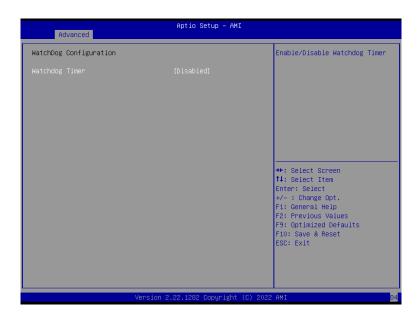

| DFI WDT Configuration                                                                                           | 35<br>36 |

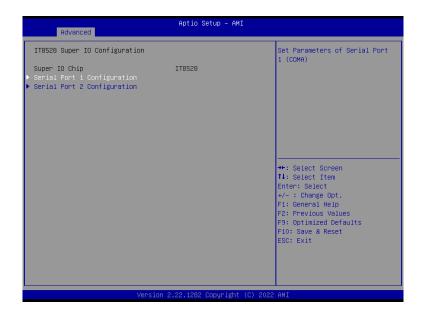

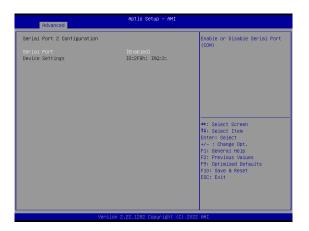

| IT8528 Super IO Configuration                                                                                   | 36       |

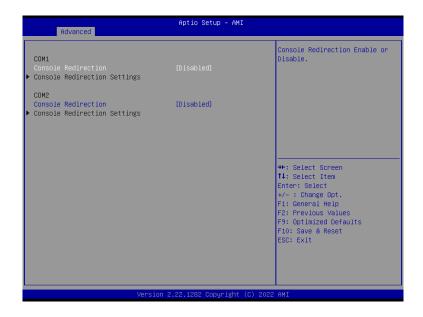

| Serial Port Console Redirection                                                                                 | 37       |

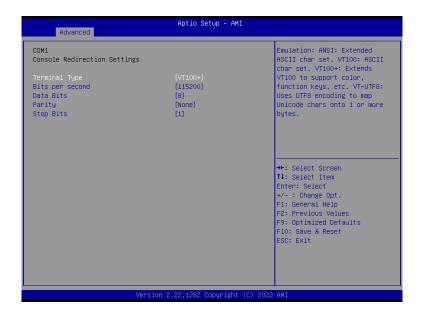

| Serial Port Console Redirection ► Console Redirection Settings                                                  | 37<br>ຊຄ |

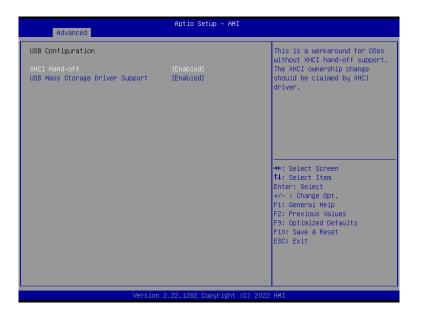

| USB Configuration                                                                                               | 38       |

| Chipset                                                                                                         |          |

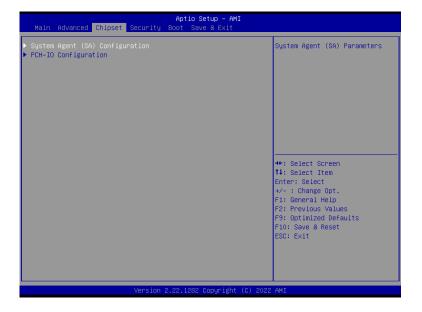

| System Agent (SA) Configuration                                                                                 | 39       |

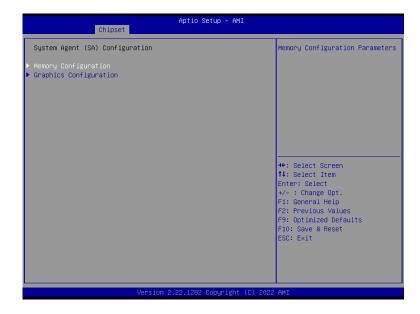

| System Agent (SA) Configuration   Memory Configuration  System Agent (SA) Configuration  Graphics Configuration | 40       |

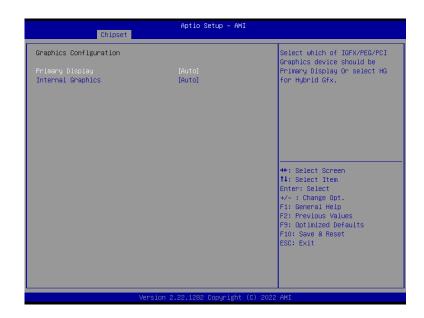

| System Agent (SA) Configuration ► Graphics Configuration                                                        | 40       |

| PCH-IO Configuration                             | 41 |

|--------------------------------------------------|----|

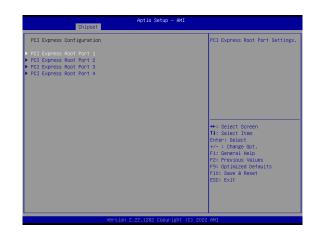

| PCH-IO Configuration ▶ PCI Express Configuration | 41 |

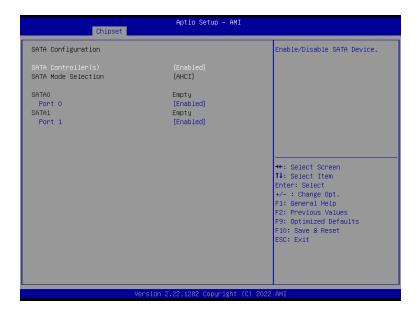

| PCH-IO Configuration ► SATA Configuration        | 42 |

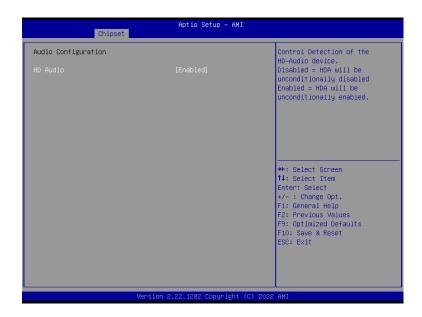

| PCH-IO Configuration ► Audio Configuration       | 42 |

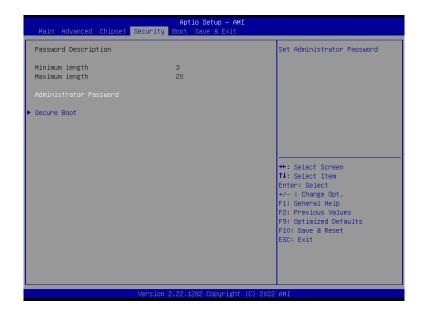

| Security                                         | 43 |

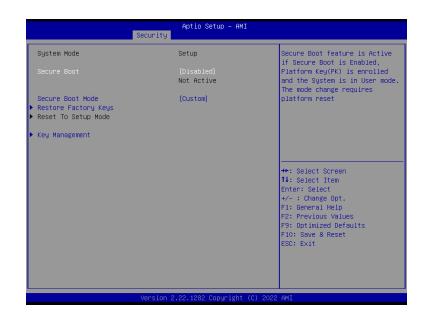

| Secure Boot                                      | 43 |

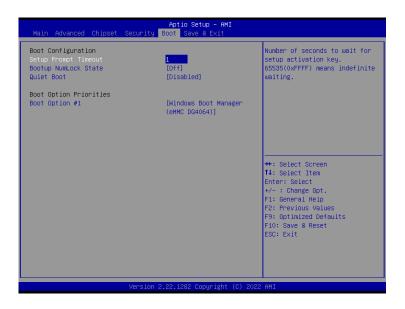

| Boot                                             | 44 |

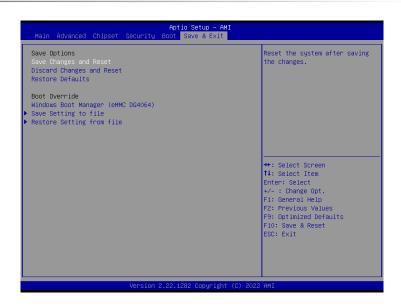

| Save & Exit                                      | 44 |

| Updating the BIOS                                | 45 |

| Notice: BIOS SPI ROM                             | 45 |

## **About this Manual**

This manual can be downloaded from the website.

The manual is subject to change and update without notice, and may be based on editions that do not resemble your actual products. Please visit our website or contact our sales representatives for the latest editions.

## Warranty

- Warranty does not cover damages or failures that occur from misuse of the product, inability to use the product, unauthorized replacement or alteration of components and product specifications.

- The warranty is void if the product has been subjected to physical abuse, improper installation, modification, accidents or unauthorized repair of the product.

- Unless otherwise instructed in this user's manual, the user may not, under any circumstances, attempt to perform service, adjustments or repairs on the product, whether in or out of warranty. It must be returned to the purchase point, factory or authorized service agency for all such work.

- We will not be liable for any indirect, special, incidental or consequential damages to the product that has been modified or altered.

## **Static Electricity Precautions**

It is quite easy to inadvertently damage your PC, system board, components or devices even before installing them in your system unit. Static electrical discharge can damage computer components without causing any signs of physical damage. You must take extra care in handling them to ensure against electrostatic build-up.

- To prevent electrostatic build-up, leave the system board in its anti-static bag until you are ready to install it.

- Wear an antistatic wrist strap.

- Do all preparation work on a static-free surface.

- Hold the device only by its edges. Be careful not to touch any of the components, contacts or connections.

- Avoid touching the pins or contacts on all modules and connectors. Hold modules or connectors by their ends.

#### Important:

Electrostatic discharge (ESD) can damage your processor, disk drive and other components. Perform the upgrade instruction procedures described at an ESD workstation only. If such a station is not available, you can provide some ESD protection by wearing an antistatic wrist strap and attaching it to a metal part of the system chassis. If a wrist strap is unavailable, establish and maintain contact with the system chassis throughout any procedures requiring ESD protection.

## **Safety Measures**

- To avoid damage to the system, use the correct AC input voltage range.

- To reduce the risk of electric shock, unplug the power cord before removing the system chassis cover for installation or servicing. After installation or servicing, cover the system chassis before plugging the power cord.

## **About the Package**

The package contains the following items. If any of these items are missing or damaged, please contact your dealer or sales representative for assistance.

The accessories in the package may not come similar to the information listed below. This may differ in accordance with the sales region or models in which it was sold. For more information about the standard package in your region, please contact your dealer or sales representative.

- Heat Sink (For IHS package CPU)

- · Heat Sink (For BARE-DIE CPU)

- Cooler (For IHS packages CPU with wide temperature environment.)

- \* IHS: Integrated Heat Spreader

## **Optional Items**

The board and accessories in the package may not come similar to the information listed above. This may differ in accordance with the sales region or models in which it was sold. For more information about the standard package in your region, please contact your dealer or sales representative.

## **Before Using the System Board**

Before using the system board, prepare basic system components. If you are installing the system board in a new system, you will need at least the following internal components.

· Storage devices such as hard disk drive, etc.

You will also need external system peripherals you intend to use which will normally include at least a keyboard, a mouse and a video display monitor.

# **Chapter 1 - Introduction**

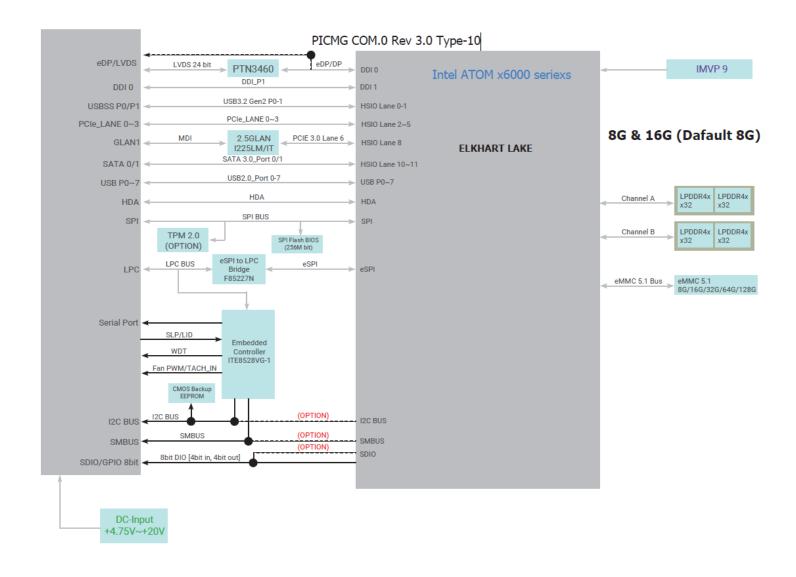

# **▶** Specification

| SYSTEM    | Processor  | Intel Atom <sup>®</sup> x6000 series and Intel <sup>®</sup> Celeron <sup>®</sup> and Pentium <sup>®</sup> N & J series processors (formerly Code name "Elkhart Lake")                                                                      |

|-----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Memory     | LPDDR4X max up to 16GB within dual channel and maximum speed depends on SOC. (The LPDDR4X speed ≤ 3733 MT/s (2RPC/1RPC) and 4267 MT/s (1RPC) which depends on processor.)                                                                  |

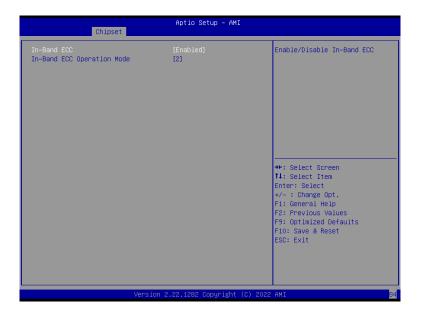

|           |            | Note: • 8GB/16GB supported by project basis. • In-band ECC (IBECC) with normal memory chip support on selected ATOM x6000 series SKUs. IBECC can set enabled or disabled in BIOS setup menu.                                               |

|           | BIOS       | AMI SPI 256Mbit                                                                                                                                                                                                                            |

| GRAPHICS  | Controller | Intel® HD Graphics                                                                                                                                                                                                                         |

|           | Feature    | OpenGL 5.0, DirectX 12, OpenCL 2.1<br>HW Decode: AVC/H.264, MPEG2, VC1, WMV9, JPEG/MJPEG, HEVC/H.265, VP8, VP9, MVC<br>HW Encode: AVC/H.264, JPEG/MJPEG, HEVC/H.265, VP9, MVC                                                              |

|           | Display    | 1 x DDI<br>1 x LVDS/eDP<br>LVDS: single channel 24-bit, resolution up to 1920x1200 @ 60Hz<br>eDP: resolution up to 4096x2160 @ 60Hz<br>HDMI: resolution up to 4096x2160 @ 30Hz<br>DP++: resolution up to 4096x2160 @ 60Hz, 3840x2160 @60Hz |

| EXPANSION | Interface  | 4 x PCIe x1 (Gen 3) 1 x SD/SDIO (available upon request) 1 x I2C 1 x SMBus 1 x LPC 1 x Speaker 1 x SPI 2 x UART (TX/RX)                                                                                                                    |

| AUDIO     | Interface  | HD Audio                                                                                                                                                                                                                                   |

| ETHERNET  | Controller | 1 x Intel® I225IT / I225-LM (10/100/1000Mbps/2.5Gbps)                                                                                                                                                                                      |

| I/O       | USB        | 2 x USB 3.1 Gen2<br>8 x USB 2.0                                                                                                                                                                                                            |

|           | SATA       | 2 x SATA 3.0 (up to 6Gb/s)                                                                                                                                                                                                                 |

|           | eMMC       | 1 x 8GB/16GB/32GB/64GB*/128GB eMMC 5.1 (available upon request)                                                                                                                                                                            |

|           | DIO        | 1 x 8-bit DIO                                                                                                                                                                                                                              |

|           |            |                                                                                                                                                                                                                                            |

| WATCHDOG TIMER               | Output & Interval         | System Reset, Programmable via Software from 1 to 255 Seconds       |

|------------------------------|---------------------------|---------------------------------------------------------------------|

| SECURITY                     | TPM                       | dTPM or fTPM (Opational)                                            |

| Power                        | Туре                      | 4.75V~20V, 5VSB, VCC_RTC (ATX mode)<br>4.75V~20V, VCC_RTC (AT mode) |

|                              | Consumption               | TBD                                                                 |

| OS SUPPORT                   | OS Support (UEFI<br>Only) | Windows: Windows 10 IoT Enterprise 64-bit<br>Linux                  |

| ENVIRONMENT                  | Temperature               | Operating: -5 to 65°C, -40 to 85°C<br>Storage: -40 to 85°C          |

|                              | Humidity                  | Operating: 5 to 90% RH<br>Storage: 5 to 90% RH                      |

|                              | MTBF                      | TBD                                                                 |

| MECHANICAL                   | Dimensions                | COM Express® Mini 84mm (3.3") x 55mm (2.16")                        |

|                              | Compliance                | PICMG COM Express® R3.0, Type 10                                    |

| STANDARDS AND CERTIFICATIONS | Certification             | CE, FCC                                                             |

## **Chapter 2 - Concept**

## **▶** COM Express Module Standards

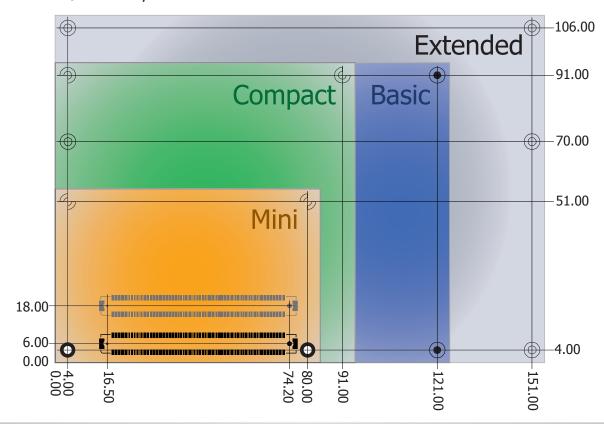

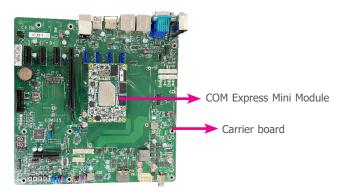

The figure below shows the dimensions of the different types of COM Express modules. EHL9A2 is a COM Express Mini. The dimension is 84mm x 55mm.

- O Common for all Form Factors

- Extended only

- Basic only

- **©** Compact only

- Compact and Basic only

- <sup>Q</sup>

<sub>O</sub> Mini only

## **Chapter 3 - Hardware Installation**

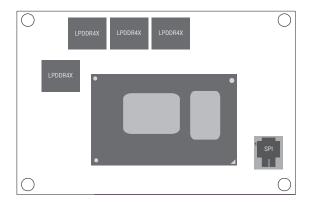

## **▶** Board Layout

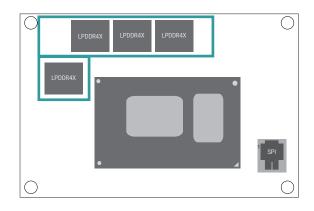

TOP VIEW

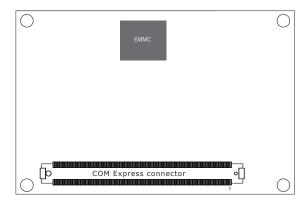

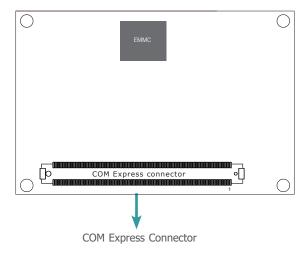

**BOTTOM VIEW**

## **▶** System Memory

The system board is equipped with LPDDR4X memory chips onboard.

#### Important:

Boards, and other components. Perform installation procedures at an ESD work-station only. If such a station is not available, you can provide some ESD protection by wearing an antistatic wrist strap and attaching it to a metal part of the system chassis. If a wrist strap is unavailable, establish and maintain contact with the system chassis throughout any procedures requiring ESD protection.

### **▶** Connector

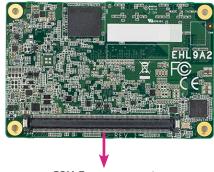

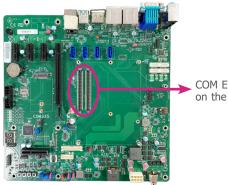

## **COM Express Connector**

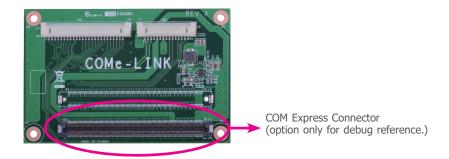

The COM Express connector is used to interface the EHL9A2 COM Express board to a carrier board. Connect the COM Express connector (located on the solder side of the board) to the COM Express connector on the carrier board. Refer to the following pages for the pin functions of the connector.

The table below shows the COM Express standard specifications and the corresponding specifications supported on the EHL9A2 module. Type 10 Modules support a single 24 bit LVDS panel interface, a single DDI and an eDP overlayed on LVDS Channel A.Two of the 8 USB ports can be used as USB 3.0.

| Connector    | Feature                    | "Type 10<br>Min / Max" | "DFI Type 10<br>EHL9A2<br>(000G)" |

|--------------|----------------------------|------------------------|-----------------------------------|

| • System I/O |                            |                        |                                   |

| A-B          | PCI Express Lanes<br>0 - 3 | 1 / 4                  | 4                                 |

| A-B          | NC-SI                      | NA                     | NA                                |

| A-B          | 1Gb LAN Port 0             | 1 / 1                  | 1                                 |

| A-B          | DDI 0                      | 0 / 1                  | 1                                 |

| A-B          | DDIs 1 - 3                 | NA                     | NA                                |

| A-B          | LVDS Channel A             | 0 / 1                  | 1                                 |

| A-B          | LVDS Channel B             | NA                     | NA                                |

| A-B          | eDP on LVDS CH A<br>pins   | 0 / 1                  | 1                                 |

| A-B          | VGA Port                   | NA                     | NA                                |

| A-B          | Serial Ports 1 - 2         | 0 / 2                  | 2                                 |

| А-В          | CAN interface on<br>SER1   | 0 / 1                  | 0                                 |

| A-B          | SATA Ports                 | 1 / 2                  | 2                                 |

| A-B          | HDA Digital Interface      | 0 / 1                  | 2                                 |

| A-B          | USB 2.0 Ports              | 4 / 8                  | 8                                 |

| A-B          | USB0 Client                | 0 / 1                  | 0                                 |

| A-B          | USB7 Client                | 0 / 1                  | 0                                 |

| A-B          | USB 3.0 Ports              | 0 / 2                  | 2                                 |

| A-B          | LPC Bus or eSPI            | 1 / 1                  | 1 LPC                             |

| A-B          | SPI (Devices)              | 1 / 2                  | 2                                 |

|              |                            |                        |                                   |

| Connector        | Feature                             | "Type 10<br>Min / Max" | "DFI Type 10<br>EHL9A2 (000G)"   |

|------------------|-------------------------------------|------------------------|----------------------------------|

| System Manage    | ement                               |                        |                                  |

| A-B <sup>6</sup> | SDIO (muxed on GPIO)                | 0 / 1                  | 1<br>(BOM option with 8 bit DIO) |

| A-B              | General Purpose I/O                 | 8 / 8                  | 8                                |

| A-B              | SMBus                               | 1 / 1                  | 1                                |

| A-B              | I2C                                 | 1 / 1                  | 1                                |

| А-В              | Watchdog Timer                      | 0 / 1                  | 1                                |

| A-B              | Speaker Out                         | 1 / 1                  | 1                                |

| A-B              | Carrier Board BIOS<br>Flash Support | 0 / 1                  | 1                                |

| A-B              | Reset Functions                     | 1 / 1                  | 1                                |

| A-B              | Trusted Platform<br>Module          | 0 / 1                  | 1                                |

| Power Manager    | ment                                |                        |                                  |

| A-B              | Thermal Protection                  | 0 / 1                  | 1                                |

| A-B              | Battery Low Alarm                   | 0 / 1                  | 1                                |

| A-B              | Suspend/Wake<br>Signals             | 0 / 3                  | 2                                |

| A-B              | Power Button Support                | 1 / 1                  | 1                                |

| A-B              | Power Good                          | 1 / 1                  | 1                                |

| A-B              | VCC_5V_SBY<br>Contacts              | 4 / 4                  | 4                                |

| A-B <sup>5</sup> | Sleep Input                         | 0 / 1                  | 1                                |

| A-B <sup>5</sup> | Lid Input                           | 0 / 1                  | 1                                |

| A-B <sup>5</sup> | Carrier Board Fan<br>Control        | 0 / 1                  | 1                                |

| Power            |                                     |                        |                                  |

| А-В              | VCC_12V Contacts                    | 12 / 12                | 12                               |

### Note for A-B<sup>5</sup>:

These signals use reclaimed VCC\_12V pins. Refer to Module base specification Section 5.8 'Protecting COM.0 Pins Reclaimed from the VCC\_12V Pool' for additional design considerations.

### Note for A-B<sup>6</sup>:

Cells in the connected columns spanning rows provide a rough approximation of features sharing connector pins.

Serial ATA activity LED. Open collector output pin driven during

SATA command activity.

## **▶** COM Express Connector Signal Description

A28

(S)ATA\_ACT#

I/O CMOS

3.3V / 3.3V

Single buffer

Pin Types I : Input to the Module O: Output from the Module

I/O : Bi-directional input / output signal

OD : Open drain output

RSVD : pins are reserved for future use and should be no connect. Do not tie the RSVD pins together.

| HDA Signals Des          | criptio     | ns                 |                          |                                     |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

|--------------------------|-------------|--------------------|--------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Signal                   | Pin#        | Pin Type           | Pwr Rail /Tolerance      | EHL9A2 PU/PD                        | Module Base Specification R3.0 Description                                                                                                                                                                                                                                                                                                                                        | COM Express Carrier Design Guide R2.0 Description                                                      |

| DA_RST#                  | A30         | O CMOS             | 3.3V Suspend/3.3V        | series 33Ω resistor                 | Reset output to CODEC, active low.                                                                                                                                                                                                                                                                                                                                                | CODEC Reset.                                                                                           |

| IDA_SYNC                 | A29         | O CMOS             | 3.3V/3.3V                | series 33Ω resistor                 | Sample-synchronization signal to the CODEC(s).                                                                                                                                                                                                                                                                                                                                    | Serial Sample Rate Synchronization.                                                                    |

| IDA_BITCLK               | A32         | I/O CMOS           | 3.3V/3.3V                | series 33Ω resistor                 | Serial data clock generated by the external CODEC(s).                                                                                                                                                                                                                                                                                                                             | 24 MHz Serial Bit Clock for HDA CODEC.                                                                 |

| IDA_SDOUT                | A33         | O CMOS             | 3.3V/3.3V                | series 33Ω resistor                 | Serial TDM data output to the CODEC.                                                                                                                                                                                                                                                                                                                                              | Audio Serial Data Output Stream.                                                                       |

| IDA_SDIN0                | B30         | I/O CMOS           | 3.3V Suspend/3.3V        |                                     |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

| HDA_SDIN1                | B29         | I/O CMOS           | 3.3V Suspend/3.3V        |                                     | Serial TDM data inputs from up to 3 CODECs.                                                                                                                                                                                                                                                                                                                                       | Audio Serial Data Input Stream from CODEC[0:2].                                                        |

| IDA_SDIN2                | B28         | I/O CMOS           | 3.3V Suspend/3.3V        | NC                                  |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

| Sigabit Ethernet         | Cianal      | a Dosavintions     |                          |                                     |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

|                          | Ť           |                    | Pwr Rail /Tolerance      | EHLOAD DIT/DD                       | Madula Paga Charification D2 0 Description                                                                                                                                                                                                                                                                                                                                        | COM Everyore Carrier Design Cuido B3 0 Description                                                     |

| ignal                    | Pin#<br>A13 | Pin Type           | -                        | EHL9A2 PU/PD                        | Module Base Specification R3.0 Description                                                                                                                                                                                                                                                                                                                                        | COM Express Carrier Design Guide R2.0 Description                                                      |

| BEO_MDIO+                | _           | I/O Analog         | 3.3V max Suspend         |                                     | Gigabit Ethernet Controller 0: Media Dependent Interface Differential                                                                                                                                                                                                                                                                                                             | Media Dependent Interface (MDI) differential pair 0.                                                   |

| BEO_MDIO-                | A12         | I/O Analog         | 3.3V max Suspend         |                                     | Pairs 0,1,2,3. The MDI can operate in 1000, 100 and 10 Mbit / sec                                                                                                                                                                                                                                                                                                                 |                                                                                                        |

| BEO_MDI1+                | A10<br>A9   | I/O Analog         | 3.3V max Suspend         |                                     | modes. Some pairs are unused in some modes, per the following:<br>1000BASE-T 100BASE-TX 10BASE-T                                                                                                                                                                                                                                                                                  | Media Dependent Interface (MDI) differential pair 1.                                                   |

| BEO_MDI1-                | _           | I/O Analog         | 3.3V max Suspend         |                                     | MDI[0]+/- B1 DA+/- TX+/- TX+/-                                                                                                                                                                                                                                                                                                                                                    |                                                                                                        |

| BEO_MDI2+                | A7          | I/O Analog         | 3.3V max Suspend         |                                     | MDI[1]+/- B1 DB+/- DY+/- DY+/-                                                                                                                                                                                                                                                                                                                                                    | Media Dependent Interface (MDI) differential pair 2. Only used for 1000Mbit/sec Gigabit Ethernet mode. |

| BEO_MDI2-                | A6          | I/O Analog         | 3.3V max Suspend         |                                     | MDI[2]+/- BI_DC+/-                                                                                                                                                                                                                                                                                                                                                                | Media Dependent Interface (MDI) differential pair 3.                                                   |

| GBEO_MDI3+<br>GBEO MDI3- | A3<br>A2    | I/O Analog         | 3.3V max Suspend         |                                     | MDI[3]+/- B1_DD+/-                                                                                                                                                                                                                                                                                                                                                                | Only used for 1000Mbit/sec Gigabit Ethernet mode.                                                      |

|                          | B2          | I/O Analog OD CMOS | 3.3V max Suspend         |                                     |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

| GBE0_ACT#                |             |                    | 3.3V Suspend/3.3V        | Only at Pin A4 or A5 link speed the | Gigabit Ethernet Controller 0 activity indicator, active low.                                                                                                                                                                                                                                                                                                                     | Ethernet controller 0 activity indicator, active low.                                                  |

| GBE0_LINK#               | A8          | OD CMOS            | 3.3V Suspend/3.3V        | GBEO_LINK# will active low.         | Gigabit Ethernet Controller 0 link indicator, active low.                                                                                                                                                                                                                                                                                                                         | Ethernet controller 0 link indicator, active low.                                                      |

| GBE0_LINK100#            | A4          | OD CMOS            | 3.3V Suspend/3.3V        | LED for link speed with 1Gbps.      | Gigabit Ethernet Controller 0 100 Mbit / sec link indicator, active low.                                                                                                                                                                                                                                                                                                          | Ethernet controller 0 100Mbit/sec link indicator, active low                                           |

| GBEO_LINK1000#           | A5          | OD CMOS            | 3.3V Suspend/3.3V        | LED for link speed with<br>2.5Gbps  | Gigabit Ethernet Controller 0 1000 Mbit / sec link indicator, active low.                                                                                                                                                                                                                                                                                                         | Ethernet controller 0 1000Mbit/sec link indicator, active lo                                           |

| GBE0_CTREF               | A14         | REF                | GND min, 3.3V max        | NC                                  | Reference voltage for Carrier Board Ethernet channel 0 magnetics center tap. The reference voltage is determined by the requirements of the Module PHY and may be as low as 0V and as high as 3.3V. The reference voltage output shall be current limited on the Module. In the case in which the reference is shorted to ground, the current shall be limited to 250 mA or less. | Reference voltage for Carrier Board Ethernet channel 0 magnetics center tap.                           |

| GBE0_SDP                 | A49         | I/O                | 3.3V Suspend/3.3V        |                                     | Gigabit Ethernet Controller 0 Software-Definable Pin.<br>Can also be used for IEEE1588 support such as a 1pps signal.                                                                                                                                                                                                                                                             |                                                                                                        |

| SATA Signals Des         | criptio     | ons                |                          |                                     |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

| ignal                    | Pin#        | Pin Type           | Pwr Rail /Tolerance      | EHL9A2 PU/PD                        | Module Base Specification R3.0 Description                                                                                                                                                                                                                                                                                                                                        | COM Express Carrier Design Guide R2.0 Description                                                      |

| SATA0_TX+                | A16         | O SATA             | AC coupled on Module     | AC Coupling capacitor               | ·                                                                                                                                                                                                                                                                                                                                                                                 | Serial ATA channel 0                                                                                   |

| ATA0_TX-                 | A17         | O SATA             | AC coupled on Module     | AC Coupling capacitor               | Serial ATA or SAS Channel 0 transmit differential pair.                                                                                                                                                                                                                                                                                                                           | Transmit output differential pair.                                                                     |

| ATA0_RX+                 | A19         | I SATA             | AC coupled on Module     | AC Coupling capacitor               |                                                                                                                                                                                                                                                                                                                                                                                   | Serial ATA channel 0                                                                                   |

| ATAO RX-                 | A20         | I SATA             | AC coupled on Module     | AC Coupling capacitor               | Serial ATA or SAS Channel 0 receive differential pair.                                                                                                                                                                                                                                                                                                                            | Receive input differential pair.                                                                       |

| ATA1 TX+                 | B16         | O SATA             | AC coupled on Module     | AC Coupling capacitor               |                                                                                                                                                                                                                                                                                                                                                                                   | Serial ATA channel 1                                                                                   |

| ATA1_TX-                 | B17         | O SATA             | AC coupled on Module     | AC Coupling capacitor               | Serial ATA or SAS Channel 1 transmit differential pair.                                                                                                                                                                                                                                                                                                                           | Transmit output differential pair.                                                                     |

| ATA1 RX+                 | B19         | I SATA             | AC coupled on Module     | AC Coupling capacitor               |                                                                                                                                                                                                                                                                                                                                                                                   | Serial ATA channel 1                                                                                   |

| ATA1_RX-                 | B20         | I SATA             | AC coupled on Module     | AC Coupling capacitor               | Serial ATA or SAS Channel 1 receive differential pair.                                                                                                                                                                                                                                                                                                                            | Receive input differential pair.                                                                       |

| ·····ɪ_iv                | 520         | 2 5, 1171          | , to coupled off Floudie | coupling capacitor                  |                                                                                                                                                                                                                                                                                                                                                                                   | <u>'</u>                                                                                               |

User's Manual | EHL9A2 13

Serial ATA (activity indicator), active low.

| PCI Express Lanes Signals Descriptions |            |          |                        |                       |                                                                     |                                                                  |  |  |

|----------------------------------------|------------|----------|------------------------|-----------------------|---------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| Signal                                 | Pin#       | Pin Type | Pwr Rail /Tolerance    | EHL9A2 PU/PD          | Module Base Specification R3.0 Description                          | COM Express Carrier Design Guide R2.0 Description                |  |  |

| PCIE_TX0+                              | A68        | O PCIE   | AC coupled on Module   | AC Coupling capacitor | PCI Express Differential Transmit Pairs 0                           | PCIe channel 0. Transmit Output differential pair.               |  |  |

| PCIE_TX0-                              | A69        | OTCL     | Ac coupled on Floduic  | AC Coupling capacitor | T CI Express Differential Transmit Falls 0                          | reference of transmit output unreferration pair.                 |  |  |

| PCIE_RX0+                              | B68        | I PCIE   | AC coupled off Module  |                       | PCI Express Differential Receive Pairs 0                            | PCIe channel 0. Receive Input differential pair.                 |  |  |

| PCIE_RX0-                              | B69        | I I CIL  | ne coupled on Floatile |                       | TOT EXPICES DIFFERENCE FUELS O                                      | Tele charmer of Receive Input amerendal pair.                    |  |  |

| PCIE_TX1+                              | A64        | O PCIE   | AC coupled on Module   | AC Coupling capacitor | PCI Express Differential Transmit Pairs 1                           | PCIe channel 1. Transmit Output differential pair.               |  |  |

| PCIE_TX1-                              | A65        | 0 . 012  | ne coupled on rioddic  | AC Coupling capacitor | TOT EXPLOSE BITCH CITICAL TRANSPIRE FAIRS 1                         | r de diamer et transmit d'atpat amerenda pant                    |  |  |

| PCIE_RX1+                              | B64        | I PCIE   | AC coupled off Module  |                       | PCI Express Differential Receive Pairs 1                            | PCIe channel 1. Receive Input differential pair.                 |  |  |

| PCIE_RX1-                              | B65        |          |                        |                       |                                                                     |                                                                  |  |  |

| PCIE_TX2+                              | A61        | O PCIE   | AC coupled on Module   | AC Coupling capacitor | PCI Express Differential Transmit Pairs 2                           | PCIe channel 2. Transmit Output differential pair.               |  |  |

| PCIE_TX2-                              | A62        |          |                        | AC Coupling capacitor | . ,                                                                 |                                                                  |  |  |

| PCIE_RX2+                              | B61        | I PCIE   | AC coupled off Module  |                       | PCI Express Differential Receive Pairs 2                            | PCIe channel 2. Receive Input differential pair.                 |  |  |

| PCIE_RX2-                              | B62        |          | · .                    | 100 11 11             | '                                                                   | · · · · · ·                                                      |  |  |

| PCIE_TX3+                              | A58        | O PCIE   | AC coupled on Module   | AC Coupling capacitor | PCI Express Differential Transmit Pairs 3                           | PCIe channel 3. Transmit Output differential pair.               |  |  |

| PCIE_TX3-                              | A59<br>B58 | +        | 1                      | AC Coupling capacitor |                                                                     | · · · · · · · · · · · · · · · · · · ·                            |  |  |

| PCIE_RX3+                              |            | I PCIE   | AC coupled off Module  |                       | PCI Express Differential Receive Pairs 3                            | PCIe channel 3. Receive Input differential pair.                 |  |  |

| PCIE_RX3-                              | B59        | -        |                        |                       |                                                                     |                                                                  |  |  |

| PCIE_CLK_REF+                          | A88        |          |                        |                       | Reference clock output for all PCI Express and PCI Express Graphics | PCIe Reference Clock for all COM Express PCIe lanes, and for PEG |  |  |

| PCIE_CLK_REF-                          | A89        | O PCIE   | PCIE                   |                       | lanes.                                                              | lanes.                                                           |  |  |

Note: For PCIe device down or slot card components on the carrier board, please use the PCIe Lane0 port first.

| USB Signals Descrip |      | I        | I                    |                         | I                                                                                                                                                                                                                                                    | January 1                                                                                                                              |

|---------------------|------|----------|----------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Signal              | Pin# | Pin Type | Pwr Rail /Tolerance  | EHL9A2 PU/PD            | Module Base Specification R3.0 Description                                                                                                                                                                                                           | COM Express Carrier Design Guide R2.0 Description                                                                                      |

| USB0+               | A46  | I/O USB  | 3.3V Suspend/3.3V    |                         | USB differential pairs, channel 0. If implemented, shall be host ports.                                                                                                                                                                              | USB Port 0, data + or D+                                                                                                               |

| USB0-               | A45  |          |                      |                         |                                                                                                                                                                                                                                                      | USB Port 0, data - or D-                                                                                                               |

| USB1+               | B46  | I/O USB  | 3.3V Suspend/3.3V    |                         | USB differential pairs, channel 1. If implemented, shall be host ports.                                                                                                                                                                              | USB Port 1, data + or D+                                                                                                               |

| USB1-               | B45  | 1/0 035  | 3.3v Suspena/3.5v    |                         | osb directidal pails, citaline 1. If imperienced, shall be nost ports.                                                                                                                                                                               | USB Port 1, data - or D-                                                                                                               |

| USB2+               | A43  | I/O USB  | 3.3V Suspend/3.3V    |                         | USB differential pairs, channel 2. If implemented, shall be host ports.                                                                                                                                                                              | USB Port 2, data + or D+                                                                                                               |

| USB2-               | A42  | 1/0 036  | 3.3V Suspenu/3.3V    |                         | 1000 differential pairs, Chairner 2. If implemented, shall be nost ports.                                                                                                                                                                            | USB Port 2, data - or D-                                                                                                               |

| USB3+               | B43  | I/O USB  | 2.2V Cum and /2.2V   |                         | LICE differential using about 2. If implemented about he heat next                                                                                                                                                                                   | USB Port 3, data + or D+                                                                                                               |

| USB3-               | B42  | 1/U USB  | 3.3V Suspend/3.3V    |                         | USB differential pairs, channel 3. If implemented, shall be host ports.                                                                                                                                                                              | USB Port 3, data - or D-                                                                                                               |

| USB4+               | A40  | I/O USB  | 2 21/ Cum and /2 21/ |                         | USB differential pairs, channel 4. If implemented, shall be host ports.                                                                                                                                                                              | USB Port 4, data + or D+                                                                                                               |

| USB4-               | A39  | 1/U USB  | 3.3V Suspend/3.3V    |                         |                                                                                                                                                                                                                                                      | USB Port 4, data - or D-                                                                                                               |

| USB5+               | B40  | I/O USB  | 2 21/ 6              |                         | USB differential pairs, channel 5. If implemented, shall be host ports.                                                                                                                                                                              | USB Port 5, data + or D+                                                                                                               |

| USB5-               | B39  | 1/U USB  | 3.3V Suspend/3.3V    |                         |                                                                                                                                                                                                                                                      | USB Port 5, data - or D-                                                                                                               |

| USB6+               | A37  | T/O LICE | 2 21/ 6              |                         | UCD differential paties showed C. Trianglement of shall be been set                                                                                                                                                                                  | USB Port 6, data + or D+                                                                                                               |

| USB6-               | A36  | I/O USB  | 3.3V Suspend/3.3V    |                         | USB differential pairs, channel 6. If implemented, shall be host ports.                                                                                                                                                                              | USB Port 6, data - or D-                                                                                                               |

| USB7+               | B37  |          |                      |                         |                                                                                                                                                                                                                                                      | USB Port 7, data + or D+                                                                                                               |

| USB7-               | B36  | I/O USB  | 3.3V Suspend/3.3V    |                         | USB differential pairs, channel 7. If implemented, shall be host ports.                                                                                                                                                                              | USB Port 7, data - or D-                                                                                                               |

| USB_0_1_OC#         | B44  | I CMOS   | 3.3V Suspend/3.3V    | PU 10KΩ to 3.3V Suspend | USB over-current sense, USB channels 0 and 1. A pull-up for this line shall be present on the Module. An open drain driver from a USB current monitor on the Carrier Board may drive this line low. Do not pull this line high on the Carrier Board. | USB over-current sense, USB ports 0 and 1. Do not pull up these lines to 3.3V on the Carrier Board – this shall be done on the Module. |

| USB_2_3_OC#              | A44      | I CMOS   | 3.3V Suspend/3.3V             | PU 10KΩ to 3.3V Suspend                          | USB over-current sense, USB channels 2 and 3.  A pull-up for this line shall be present on the Module.  An open drain driver from a USB current monitor on the Carrier Board may drive this line low.  Do not null this line high on the Carrier Board.                                                  | USB over-current sense, USB ports 2 and 3. Do not pull up these lines to 3.3V on the Carrier Board – this shall be done on the Module.       |  |

|--------------------------|----------|----------|-------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| USB_4_5_OC#              | B38      | I CMOS   | 3.3V Suspend/3.3V             | PU 10KΩ to 3.3V Suspend                          | Do not null this line high on the Carrier Roard. USB over-current sense, USB channels 4 and 5.  A pull-up for this line shall be present on the Module.  An open drain driver from a USB current monitor on the Carrier Board may drive this line low.  Do not null this line high on the Carrier Board. | USB over-current sense, USB ports 4 and 5. Do not pull up these lines to 3.3V on the Carrier Board – this shall be done on the Module.       |  |

| USB_6_7_OC#              | A38      | I CMOS   | 3.3V Suspend/3.3V             | PU $10 \text{K}\Omega$ to $3.3 \text{V}$ Suspend | USB over-current sense, USB channels 6 and 7.  A pull-up for this line shall be present on the Module.  An open drain driver from a USB current monitor on the Carrier Board may drive this line low.  Do not pull this line high on the Carrier Board.                                                  | USB over-current sense, USB ports 6 and 7.<br>Do not pull up these lines to 3.3V on the Carrier Board – this shall be<br>done on the Module. |  |

| USB_SSTX0+               | B23      |          |                               | AC Coupling capacitor                            |                                                                                                                                                                                                                                                                                                          | USB Port 0, SuperSpeed TX +                                                                                                                  |  |

| USB_SSTX0-               | B22      | O PCIE   | AC coupled on Module          | AC Coupling capacitor                            | -Additional transmit signal differential pairs for the SuperSpeed USB data path.                                                                                                                                                                                                                         | USB Port 0, SuperSpeed TX -                                                                                                                  |  |

| USB_SSRX0+               | A23      |          |                               |                                                  |                                                                                                                                                                                                                                                                                                          | USB Port 0, SuperSpeed RX +                                                                                                                  |  |

| USB_SSRX0-               | A22      | I PCIE   | AC coupled off Module         |                                                  | Additional receive signal differential pairs for the SuperSpeed USB data path.                                                                                                                                                                                                                           | USB Port 0, SuperSpeed RX -                                                                                                                  |  |

| USB_SSTX1+               | B26      | 0.0075   | AC coupled on Module          | AC Coupling capacitor                            | Additional transmit signal differential pairs for the SuperSpeed USB data path.                                                                                                                                                                                                                          | USB Port 1, SuperSpeed TX +                                                                                                                  |  |

| USB_SSTX1-               | B25      | O PCIE   |                               | AC Coupling capacitor                            |                                                                                                                                                                                                                                                                                                          | USB Port 1, SuperSpeed TX -                                                                                                                  |  |

| USB_SSRX1+               | A26      | I DOIE   | AC coupled off Module         |                                                  | Additional receive signal differential pairs for the SuperSpeed USB data path.                                                                                                                                                                                                                           | USB Port 1, SuperSpeed RX +                                                                                                                  |  |

| USB_SSRX1-               | A25      | I PCIE   |                               |                                                  |                                                                                                                                                                                                                                                                                                          | USB Port 1, SuperSpeed RX -                                                                                                                  |  |

| USB0_HOST_PRSNT          | B48      | I CMOS   | 3.3V Suspend/3.3V             | N.C.                                             | Module USB client may detect the presence of a USB host on USB0. A high value indicates that a host is present.                                                                                                                                                                                          |                                                                                                                                              |  |

| USB7_HOST_PRSNT          | B96      | I CMOS   | 3.3V Suspend/3.3V             | N.C.                                             | Module USB client may detect the presence of a USB host on USB7. A high value indicates that a host is present.                                                                                                                                                                                          |                                                                                                                                              |  |

| LVDS Signals Description | <u> </u> |          |                               |                                                  |                                                                                                                                                                                                                                                                                                          |                                                                                                                                              |  |

| Signal                   | Pin#     | Pin Type | Pwr Rail /Tolerance           | EHL9A2 PU/PD                                     | Module Base Specification R3.0 Description                                                                                                                                                                                                                                                               | COM Express Carrier Design Guide R2.0 Description                                                                                            |  |

| LVDS_A0+/eDP_TX2+        | A71      | O LVDS   | LVDS<br>EDP: AC coupled off   |                                                  |                                                                                                                                                                                                                                                                                                          | LVDS channel A differential signal pair 0                                                                                                    |  |

| LVDS_A0-/eDP_TX2-        | A72      | O LVDS   | Module Module                 |                                                  |                                                                                                                                                                                                                                                                                                          | eDP lane 2, TX± differential signal pair                                                                                                     |  |

| LVDS_A1+/eDP_TX1+        | A73      | O LVDS   | LVDS<br>EDP: AC coupled off   |                                                  |                                                                                                                                                                                                                                                                                                          | LVDS channel A differential signal pair 1                                                                                                    |  |

| LVDS_A1-/eDP_TX1-        | A74      | O LVD3   | Module                        |                                                  | LVDS Channel A differential pairs                                                                                                                                                                                                                                                                        | eDP lane 1, TX± differential signal pair                                                                                                     |  |

| LVDS_A2+/eDP_TX0+        | A75      | O LVDS   | LVDS<br>EDP: AC coupled off   |                                                  | eDP: eDP differential pairs                                                                                                                                                                                                                                                                              | LVDS channel A differential signal pair 2                                                                                                    |  |

| LVDS_A2-/eDP_TX0-        | A76      | O LVD3   | Module                        |                                                  |                                                                                                                                                                                                                                                                                                          | eDP lane 0, TX± differential signal pair                                                                                                     |  |

| LVDS_A3+                 | A78      | O LVDS   | LVDS                          |                                                  |                                                                                                                                                                                                                                                                                                          | IVDS channel A differential cignal pair 3                                                                                                    |  |