## **User Manual**

## **MIO-2364**

Intel® Core™ i3-N305 Processor,

Intel® N-Series Processor, and

Intel® Atom™ x7000E Series

Processor

2.5" Pico-ITX SBC

(Code name: Alder Lake N)

## Copyright

The documentation and the software included with this product are copyrighted 2024 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated, or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. The information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties that may result from its use.

## **Acknowledgments**

Intel® is a trademark of Intel® Corporation.

AMI is a trademark of American Megatrends, Inc.

IBM, PC, PS/2, and VGA are trademarks of International Business Machines Corporation.

Microsoft Windows<sup>®</sup> and DirectX<sup>®</sup> are registered trademarks of Microsoft Corp.

All other product names or trademarks are properties of their respective owners.

For more information on this and other Advantech products, please visit our websites at:

http://www.advantech.com

http://www.advantech.com/eplatform

For technical support and service, please visit our support website at:

http://support.advantech.com/

This manual is for the MIO-2364.

#### **Product Warranty (2 Years)**

Advantech warrants the original purchaser that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products that have been repaired or altered by persons other than repair personnel authorized by Advantech, or products that have been subject to misuse, abuse, accident, or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced free of charge during the warranty period. For out-of-warranty repairs, customers will be billed according to the cost of replacement materials, service time, and freight. Please consult your dealer for more details.

If you believe your product to be defective, follow the steps outlined below.

- 1. Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages displayed when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- 3. If your product is diagnosed as defective, obtain a return merchandise authorization (RMA) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a completed Repair and Replacement Order Card, and a proof of purchase date (such as a photocopy of your sales receipt) into a shippable container. Products returned without a proof of purchase date are not eligible for warranty service.

- 5. Write the RMA number clearly on the outside of the package and ship the package prepaid to your dealer.

## **Declaration of Conformity**

#### CE

This product has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This type of cable is available from Advantech. Please contact your local supplier for ordering information.

Test conditions for passing also include the equipment being operated within an industrial enclosure. In order to protect the product from damage caused by electrostatic discharge (ESD) and EMI leakage, we strongly recommend the use of CEcompliant industrial enclosure products.

#### **FCC Class B**

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for assistance.

Caution! There is danger of a new battery exploding if it is incorrectly installed. Do not attempt to recharge, force open, or heat the battery. Replace the battery only with the same or equivalent type recommended by the manflatterer. Discard used batteries according to the manufacturer's instructions.

#### **Technical Support and Assistance**

- Visit the Advantech website at www.advantech.com/support to obtain the latest product information.

- 2. Contact your distributor, sales representative, or Advantech's customer service center for technical support if you need additional assistance. Please have the following information ready before calling:

- Product name and serial number

- Description of your peripheral attachments

- Description of your software (operating system, version, application software, etc.)

- A complete description of the problem

- The exact wording of any error messages

## **Packing List**

Before you begin installing your card, please make sure that the following materials have been shipped:

| 1 x MIO-2364 SBC                   |                       |

|------------------------------------|-----------------------|

| 1 x SATA Cable 30cm                | (P/N: 1700006291)     |

| 1 x SATA Power Cable 15cm          | (P/N: 1700027546-01)  |

| 1 x USB 2.0 Cable 20cm             | (P/N: 1700030406-01)  |

| 1 x Audio Cable 20cm               | (P/N: 1700019584-01)  |

| 2 x COM RS-232/422/485 Cables 20cm | (P/N: 1700030404-01)  |

| 1 x AT Power Cable 12 cm           | (P/N: 1700019705-01)  |

| 1 x Active Cooler for 15W          | (P/N: 1970005708T001) |

| 1 x Passive Heatsink for 12W/6W    | (P/N: 1970005779T001) |

| 1 x Startup Manual                 | (P/N: 2046236400)     |

| 4 x Screw Kits                     | (P/N: 96662364000)    |

| 1 x DeviceOn Package               |                       |

If any of these items are missing or damaged, contact your distributor or sales representative immediately.

## **Optional Accessories**

| Part number   | Description                    |

|---------------|--------------------------------|

| TBU           | Heat spreader for the MIO-2364 |

| 1700034783-01 | PoE/PD IN cable                |

| 1700034784-01 | PoE/PD OUT cable               |

## **Contents**

| Chapter | 1                                       | Ger                   | neral Information                                                 | 1  |

|---------|-----------------------------------------|-----------------------|-------------------------------------------------------------------|----|

|         | 1.1                                     | Introdu               | ction                                                             | 2  |

|         | 1.2                                     | Specifi               | cations                                                           |    |

|         | 4.0                                     | <b>5</b>              | Table 1.1: Specifications                                         |    |

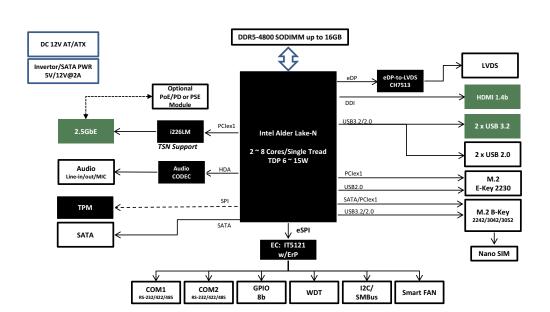

|         | 1.3                                     | Block [               | Diagram                                                           | 4  |

| Chapter | 2                                       | Med                   | chanical                                                          | 5  |

|         | 2.1                                     | Introdu               | ction                                                             | 6  |

|         | 2.2                                     | Board                 | Layout: Dimensions                                                |    |

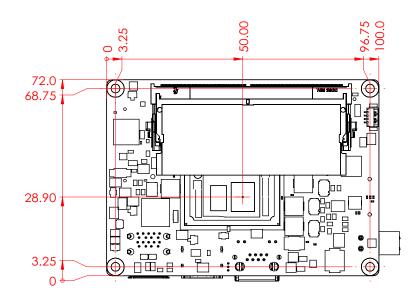

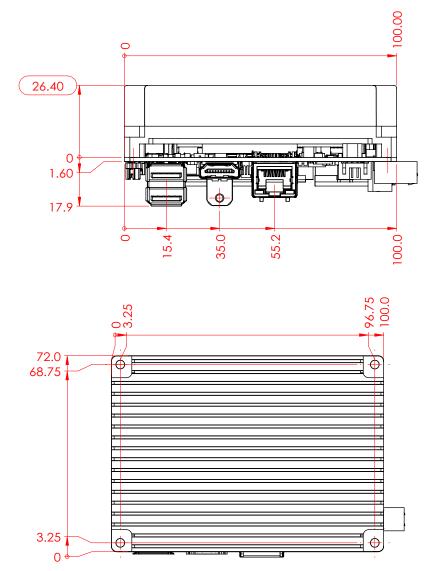

|         |                                         |                       | Figure 2.1 MIO-2364 Mechanical Drawing (Top Side)                 |    |

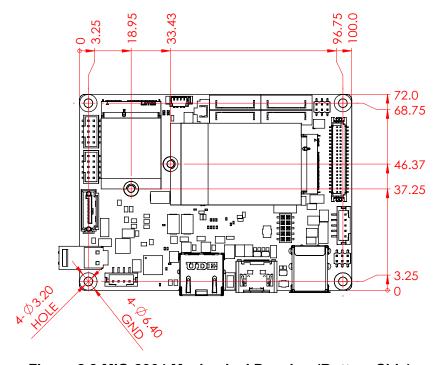

|         |                                         |                       | Figure 2.2 MIO-2364 Mechanical Drawing (Bottom Side)              |    |

|         |                                         |                       | Figure 2.3 MIO-2364 Mechanical Drawing (Coastline)                |    |

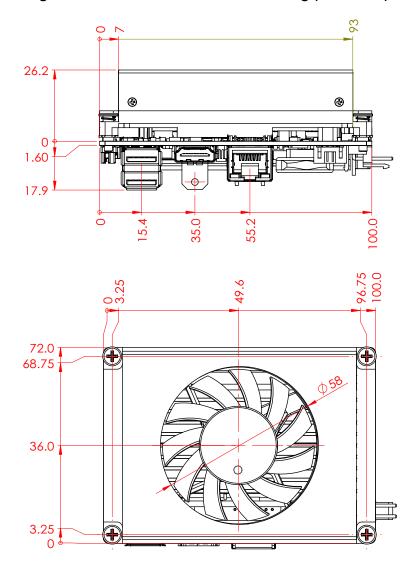

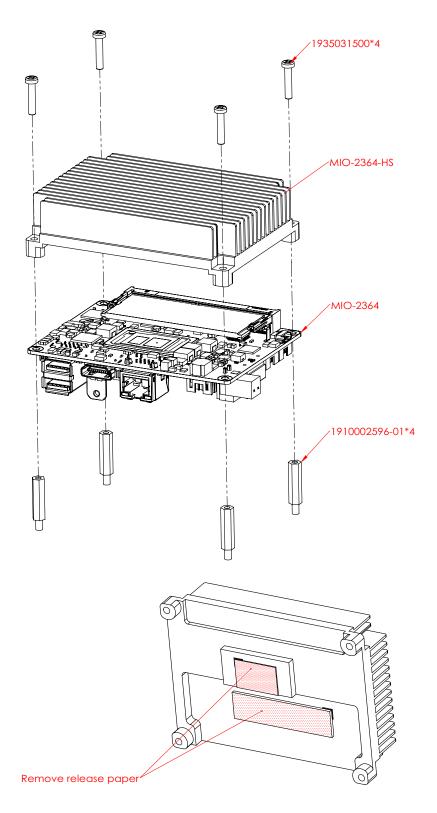

|         |                                         |                       | Figure 2.5 MIO-2364 Mechanical Drawing (with Heatsink)            |    |

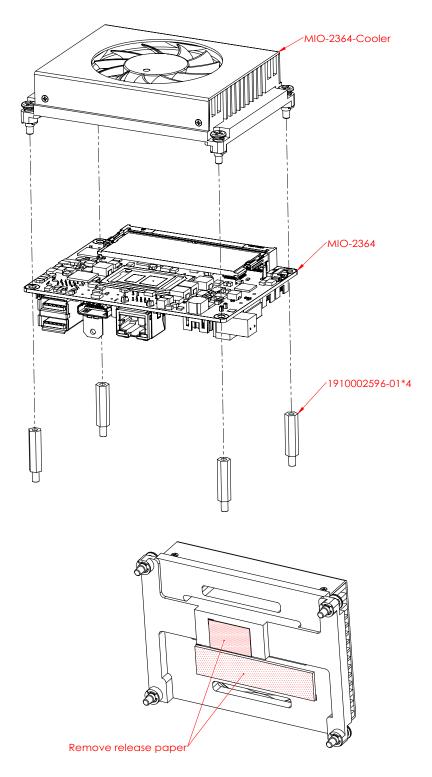

|         | 2.3                                     | Quick I               | nstallation Guide                                                 |    |

|         | 2.0                                     | 2.3.1                 | Cooler                                                            |    |

|         |                                         | 2.3.2                 | Heatsink                                                          |    |

| Chapter | 3                                       | Inst                  | allation                                                          | 11 |

|         | 3.1                                     | Jumpe                 | rs & Switches                                                     | 12 |

|         | • • • • • • • • • • • • • • • • • • • • | • • · · · · · · · · · | Table 3.1: Jumpers & Switches                                     |    |

|         | 3.2                                     | Conne                 | ctors                                                             |    |

|         |                                         |                       | Table 3.2: Connectors                                             | 12 |

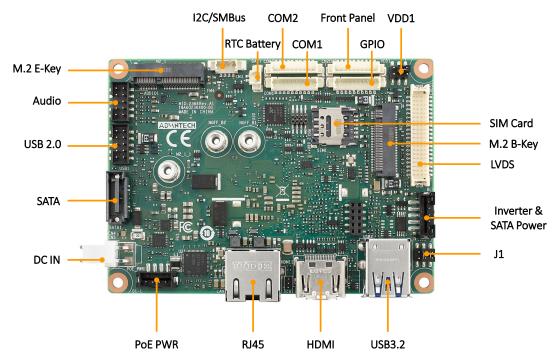

|         | 3.3                                     | Locatir               | g Connectors                                                      |    |

|         |                                         |                       | Figure 3.1 MIO-2364 Connector Locations (Top Side)                |    |

|         |                                         | <b>.</b>              | Figure 3.2 MIO-2364 Connector Locations (Bottom Side)             |    |

|         | 3.4                                     | _                     | Jumpers                                                           |    |

|         |                                         | 3.4.1                 | Panel Voltage Selection Jumper: VDD1                              |    |

|         |                                         | 3.4.2                 | AT Mode / Load BIOS default: J1                                   |    |

|         |                                         | 0.7.2                 | Table 3.4: AT Mode / Load BIOS default: J1                        |    |

|         | 3.5                                     | Conne                 | ctors (Internal)                                                  |    |

|         |                                         | 3.5.1                 | Smart FAN Internal Connector: FAN                                 |    |

|         |                                         |                       | Table 3.5: Smart FAN Internal Connector: FAN                      | 15 |

|         |                                         | 3.5.2                 | M.2 E-Key Connector: M2_1                                         | 15 |

|         |                                         |                       | Table 3.6: M.2 E-Key Connector: M2_1                              | 15 |

|         |                                         | 3.5.3                 | I2C Internal Connector: CN3                                       |    |

|         |                                         | 254                   | Table 3.7: I2C Internal Connector: CN3                            |    |

|         |                                         | 3.5.4                 | RTC Battery Connector: BAT1Table 3.8: RTC battery Connector: BAT1 |    |

|         |                                         | 3.5.5                 | COM-Port Internal Connector 1: COM1                               |    |

|         |                                         | 3.3.3                 | Table 3.9: COM-Port Internal Connector 1: COM1                    |    |

|         |                                         | 3.5.6                 | COM-Port Internal Connector 2: COM2                               |    |

|         |                                         | 0.0.0                 | Table 3.10: COM-Port Internal Connector 2: COM2                   |    |

|         |                                         | 3.5.7                 | Front Panel Internal Connector: CN1                               |    |

|         |                                         |                       | Table 3.11: Front Panel Internal Connector: CN1                   | 19 |

|         |                                         | 3.5.8                 | GPIO Internal Connector: CN2                                      |    |

|         |                                         | ·                     | Table 3.12:GPIO Internal Connector: CN2                           |    |

|         |                                         | 3.5.9                 | M.2 B-Key Connector: M2_B1                                        |    |

|         |                                         | 2 5 40                | Table 3.13:M.2 B-Key Connector: M2_B1LVDS Connector: LVDS1        |    |

|         |                                         | ა.ⴢ. 10               | LVD3 COIIIECIOI. LVD3 I                                           | ∠∠ |

|          |     | Table 3.14:LVDS Connector: I         | LVDS1                    | . 22 |

|----------|-----|--------------------------------------|--------------------------|------|

|          |     | 3.5.11 Panel Inverter Connector: BL1 |                          | . 23 |

|          |     |                                      | inector: BL1             |      |

|          |     | 3.5.12 Panel Inverter Connector: POI | E_PWR1                   | . 23 |

|          |     |                                      | inector: POE_PWR1        |      |

|          |     | 3.5.13 DC Power Input Connector (18  |                          |      |

|          |     |                                      | onnector (180D): CN4     |      |

|          |     | 3.5.14 DC Power Input Connector (90  |                          |      |

|          |     | •                                    | onnector (90D): CN5      |      |

|          |     | 3.5.15 USB 2.0 Dual-Port Internal Co |                          |      |

|          | 3.6 |                                      | Internal Connector: USB1 |      |

|          | 3.0 | Audio Internal Connector: AUDIO1     | nector: AUDIO1           |      |

| Chapter  | 4   | AMI BIOS Setup                       | 9                        | 27   |

| onaptor  | -   | Am Bioo octupiiiii                   |                          |      |

|          | 4.1 | Entering Setup                       |                          | . 29 |

|          |     | 4.1.1 Main Setup                     |                          | . 29 |

|          |     |                                      | nb                       |      |

|          |     |                                      |                          |      |

|          |     |                                      |                          |      |

|          |     |                                      |                          |      |

|          |     | 4.1.6 Save & Exit                    |                          | . 63 |

| Appendix | хΑ  | System Assignmen                     | ts                       | 35   |

|          | A.1 | System I/O Ports                     |                          |      |

|          |     | Table A.1: System I/O Ports          |                          | . 66 |

|          | A.2 | 1st MB Memory Map                    |                          |      |

|          |     |                                      | ap                       |      |

|          | A.3 | Interrupt Assignments                |                          |      |

|          |     | Table A.3: Interrupt Assignme        | ents                     | . 67 |

## Chapter

## **General Information**

This chapter gives background information on the MIO-2364.

**Sections include:**

- Introduction

- Specifications

- Block diagram

## 1.1 Introduction

MIO-2364 utilizes the 2.5" Pico-ITX SBC form factor (compact series, 100 x 72 mm) and is powered by Intel® Core  $^{\text{TM}}$  i3-N305, Intel® N-series, or Intel® Atom  $^{\text{TM}}$  x7000E Series processors. MIO-2364 offers embedded iManager 3.0, SUSI 4.0, and WISE-DeviceOn, created by Advantech, to monitor and control system operation effectively and remotely.

## 1.2 Specifications

| <b>Table 1.1: S</b> | pecifications       |                                                                                                |                     |               |  |  |

|---------------------|---------------------|------------------------------------------------------------------------------------------------|---------------------|---------------|--|--|

|                     | Processor           | i3-N305                                                                                        | N97                 | x7211E        |  |  |

|                     | Max. Frequency      | 3.80 GHz                                                                                       | 3.60 GHz            | 3.20 GHz      |  |  |

|                     | Cores/Threads       | 8/8                                                                                            | 4/4                 | 2/2           |  |  |

| Platform            | LLC                 | 6MB                                                                                            | 6MB                 | 6MB           |  |  |

|                     | CPU TDP             | 15W                                                                                            | 12W                 | 6W            |  |  |

|                     | Chipset             | Intel® 300 Series                                                                              | Chipset (SoC Inte   | egrated)      |  |  |

|                     | BIOS                | AMI EFI 256Mbit                                                                                |                     |               |  |  |

|                     | Technology          | DDR5-4800                                                                                      |                     |               |  |  |

| Memory              | Max. Capacity       | Up to 16GB                                                                                     |                     |               |  |  |

| INIEITIOI y         | Channel/Socket      | Single Channel / One Socket                                                                    |                     |               |  |  |

|                     | ECC Support         | No                                                                                             | No                  | No            |  |  |

|                     | Controller          | Intel® UHD Grap                                                                                | hics                |               |  |  |

|                     | Max. Frequency      | 1.25 GHz                                                                                       | 1.20 GHz            | 1.00 GHz      |  |  |

| Graphics            | Execution Units     | 32                                                                                             | 24                  | 16            |  |  |

|                     | 3D/HW Acceleration  | DX12, OGL4.0, OCL1.2, HW Encode: HEVC/H265, AVC/H264, VP9, HW Decode: HEVC/H265, AVC/H264, VP9 |                     |               |  |  |

| D: 1 1/E            | LCD                 | 1 x LVDS, Dual Channel 18-/24-bit, up to 1920 x 1080                                           |                     |               |  |  |

| Display I/F         | HDMI/DP             | 1 x HDMI 1.4b, u                                                                               | p to 3840 x 2160 x  | 24bpp@20-30Hz |  |  |

|                     | Multiple Displays   | Dual simultaneou                                                                               | ıs displays with LV | DS + HDMI     |  |  |

| Ethernet            | Controller          | LAN: Intel® i226LM                                                                             |                     |               |  |  |

| Ethernet            | Speed               | 2.5 GbE                                                                                        |                     |               |  |  |

| E                   | Ethernet            | 1 x RJ-45 (optional PoE/PD, 802.3at), TSN support on x7211E only                               |                     |               |  |  |

| External I/O        | VGA/HDMI/DP         | -/1/-                                                                                          |                     |               |  |  |

|                     | USB 3.2 / USB 2.0   | 2/-                                                                                            |                     |               |  |  |

|                     | SATA                | 1 x SATA Gen III 6.0 Gbps                                                                      |                     |               |  |  |

|                     | USB 2.0             | 2                                                                                              |                     |               |  |  |

|                     | Serial Bus          | SMBus/I2C                                                                                      |                     |               |  |  |

|                     | COM Port            | 2 x RS-232/422/485                                                                             |                     |               |  |  |

| Internal I/O        | GPIO                | 8-bit general purpose input output I/O                                                         |                     |               |  |  |

| internal I/O        | Audio               | Realtek ALC888s, Line-in/Line-out/MIC                                                          |                     |               |  |  |

|                     | Inverter            | 5V/12V, 2A                                                                                     |                     |               |  |  |

|                     | Smart Fan           | 12V, 0.3A (4-wire)                                                                             |                     |               |  |  |

|                     | Front Panel Control | Power-On, Reservation Case Open                                                                | t, Buzzer, SATA LE  | D, Power LED, |  |  |

| Table 1.1: Specifications |                      |                                                                                                                  |                   |             |  |

|---------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|-------------------|-------------|--|

| Board Features            | Watchdog Timer       | 0~6553 sec                                                                                                       |                   |             |  |

|                           | TPM                  | fTPM support by Intel® Platform Trust Technology Discrete TPM 2.0 (*optional)                                    |                   |             |  |

|                           | iManager 3.0         | SW API for Hardware Monitor, Smart Fan Control,<br>Brightness Control, I2C, GPIO, WDT                            |                   |             |  |

|                           | M.2 E-Key            | 1 x E-Key 2230 (I                                                                                                | PCIe x1, USB 2.0) |             |  |

| Expansion                 | M.2 B-Key            | 1 x B-Key 2242/3042/3052 (SATA x1 or PCle x1, USB 2.0 x1, USB 3.0 x1) w/ Nano-SIM                                |                   |             |  |

|                           | Supply Voltage       | Vin: DC 12V +/- 10%; RTC Battery: Lithium 3V/<br>210mAH                                                          |                   |             |  |

|                           | Connector            | ATX 2-pin 180D, optional ATX 2-pin 90D                                                                           |                   |             |  |

| Power                     | Power Management     | AT, ATX                                                                                                          |                   |             |  |

|                           | Max. Consumption     | 55.30W(12V)                                                                                                      | 43.50W(12V)       | 24.84W(12V) |  |

|                           | Idle Consumption     | 10.38W(12V)                                                                                                      | 8.32W(12V)        | 10.33W(12V) |  |

|                           | Temperature          | Operating: Standard: 0 ~ 60°C (32 ~ 140°F)                                                                       |                   |             |  |

|                           | Temperature          | Storage: -40 ~ 85°C (-40 ~ 185°F)                                                                                |                   |             |  |

| Environment               | Humidity             | Operating: 40°C @ 95% relative humidity, non-condensing<br>Storage: 60°C @ 95% relative humidity, non-condensing |                   |             |  |

|                           | Vibration Resistance | 3.5 Grms                                                                                                         |                   |             |  |

| Certification             | EMC                  | CE, FCC Class B                                                                                                  |                   |             |  |

| Mechanical                | Dimensions           | 100 x 72 mm (3.9" x 2.8")                                                                                        |                   |             |  |

| ivieciiailicai            | Net Weight           | 75 g                                                                                                             |                   |             |  |

**Note!** Support by request.

## 1.3 Block Diagram

# Chapter

## Mechanical

This chapter provides mechanical information on the MIO-2364.

Sections include:

- Mechanical Drawings

- Assembly Drawings

## 2.1 Introduction

This chapter includes board dimensions, the standard thermal solution, and optional thermal solution along with assemby instructions.

## 2.2 Board Layout: Dimensions

Figure 2.1 MIO-2364 Mechanical Drawing (Top Side)

Figure 2.2 MIO-2364 Mechanical Drawing (Bottom Side)

Figure 2.3 MIO-2364 Mechanical Drawing (Coastline)

Figure 2.4 MIO-2364 Mechanical Drawing (with Cooler)

Figure 2.5 MIO-2364 Mechanical Drawing (with Heatsink)

#### 2.3 Quick Installation Guide

The MI/O compact form factor SBC is a new-generation SBC design with a variety of mechanical improvements. Here is the quick installation guide for our thermal design. There is a heatsink in the white box inside the package. Please assemble it by following the diagrams below. Remember to remove the plastic on the thermal pad before you assemble the mechanical parts.

#### 2.3.1 **Cooler**

COOLER -MIO-2364-Remove release paper

## 2.3.2 Heatsink

Heatsink -MIO-2364-Remove release paper

## Chapter

3

## Installation

This chapter explains the setup procedures of the MIO-2364 hardware, including instructions on setting jumpers and connecting peripherals, switches, and indicators. Be sure to read all safety precautions before you begin the installation procedure.

## 3.1 Jumpers & Switches

The MIO-2364 has a number of jumpers that allow you to configure your system to suit your application. The table below lists the functions of the various jumpers.

| Table 3.1: Jumpers & Switches |                             |

|-------------------------------|-----------------------------|

| VDD1                          | Panel Voltage Selection     |

| J1                            | AT Mode / Load BIOS Default |

## 3.2 Connectors

Onboard connectors link the MIO-2364 to external devices such as hard disk drives, or a keyboard. The table below lists the function of each of the board's connectors.

| <b>Table 3.2:</b> | Connectors |                                 |

|-------------------|------------|---------------------------------|

| No.               | Connector  | Description                     |

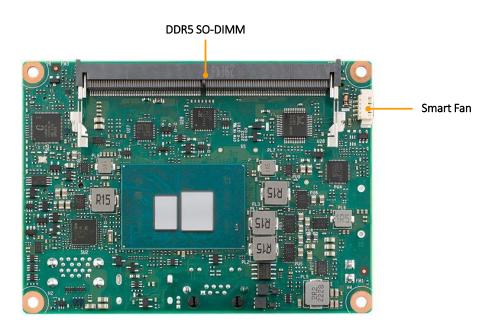

| 1                 | U17        | DDR5 SO-DIMM 9.2mm Slot         |

| 2                 | FAN1       | Smart FAN Internal Connector    |

| 3                 | M2_1       | M.2 E-Key Connector             |

| 4                 | CN3        | EC_I2C Port                     |

| 5                 | BAT1       | RTC Battery Connector           |

| 6                 | COM1       | COM Port Internal Connector 1   |

| 7                 | COM2       | COM Port Internal Connector 2   |

| 8                 | CN1        | Front Panel Internal Connector  |

| 9                 | CN2        | GPIO Internal Connector         |

| 10                | VDD1       | Panel Voltage Selection Jumper  |

| 11                | SIM1       | NANO SIM                        |

| 12                | M2_B1      | M.2 B-Key Connector             |

| 13                | LVDS1      | LVDS Panel Connector            |

| 14                | BL1        | Panel Inverter Connector        |

| 15                | J1         | AT Mode / Load BIOS default     |

| 16                | USB2       | USB 3.2 Internal Connector      |

| 17                | HDMI1      | HDMI Connector                  |

| 18                | LAN1       | RJ-45 Connector                 |

| 19                | POE_PWR1   | POE Power Connector             |

| 20                | CN4        | DC Power Input Connector (180D) |

| 21                | CN5        | DC Power Input Connector (90D)  |

| 22                | SATA1      | SATA Connector                  |

| 23                | USB1       | USB 2.0 Internal Connector      |

| 24                | AUDIO1     | Audio Internal Connector        |

| 25                | ESPI1      | ESPI Debug Port                 |

## **Locating Connectors**

Figure 3.1 MIO-2364 Connector Locations (Top Side)

Figure 3.2 MIO-2364 Connector Locations (Bottom Side)

## 3.4 Setting Jumpers

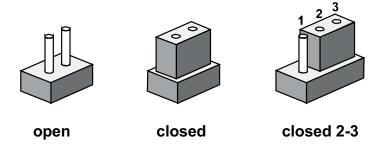

You may configure your card to match the needs of your application by setting jumpers. A jumper is a metal bridge used to close an electric circuit. It consists of two metal pins and a small metal clip (often protected by a plastic cover) that slides over the pins to connect them. To "close" a jumper, you connect the pins with the clip. To "open" a jumper, you remove the clip. Sometimes a jumper will have three pins, labeled 1, 2 and 3. In this case you would connect either pins 1 and 2, or 2 and 3.

The jumper settings are schematically depicted in this manual as follows:

A pair of needle-nose pliers may be helpful when working with jumpers. If you have any doubts about the best hardware configuration for your application, contact your local distributor or sales representative before you make any changes. Generally, you simply need a standard cable to make most connections.

#### 3.4.1 Panel Voltage Selection Jumper: VDD1

| Table 3.3: Panel | Voltage Selection Jumper: VDD1 |         |

|------------------|--------------------------------|---------|

| Jumper Short     | Panel Voltage                  |         |

| 1-3              | +3.3V (Default)                | 1 2     |

| 3-5              | +5V                            | 3 0 0 4 |

| 3-4              | +12V                           | 5 6     |

#### 3.4.2 AT Mode / Load BIOS default: J1

| Table 3.4: AT Mode / Load BIOS default: J1 |                                                                         |     |  |

|--------------------------------------------|-------------------------------------------------------------------------|-----|--|

| Jumper Short                               | Panel Function                                                          |     |  |

| 1-2                                        | AT_DET# (Default)<br>1-2 open: ATX mode<br>1-2 short: AT mode*          | 1 2 |  |

| 3-4                                        | NORMAL_BIOS (Default)                                                   |     |  |

| 5-6                                        | LOAD_BIOS_Default:<br>5-6 open: Normal*<br>5-6 short: Load BIOS Default | 5 6 |  |

## 3.5 Connectors (Internal)

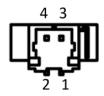

## 3.5.1 Smart FAN Internal Connector: FAN

| Table 3.5: Smart FAN Internal Connector: FAN |            |  |

|----------------------------------------------|------------|--|

| Pin Signal Pin Definition                    |            |  |

| 1                                            | GND        |  |

| 2                                            | +V12       |  |

| 3                                            | FAN_SPEED  |  |

| 4                                            | FAN_V5_PWM |  |

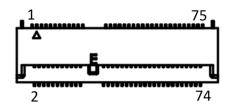

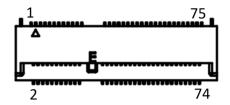

## 3.5.2 M.2 E-Key Connector: M2\_1

| <b>Table 3.6: N</b> | I.2 E-Key Connector: M2_1 |  |

|---------------------|---------------------------|--|

| Pin                 | Signal Pin Definition     |  |

| 1                   | GND                       |  |

| 2                   | +V3.3SB_M.2_E             |  |

| 3 4                 | USB8_z_P+                 |  |

| 4                   | +V3.3SB_M.2_E             |  |

| 5                   | USB8_z_P-                 |  |

| 6                   | NC                        |  |

| 7                   | GND                       |  |

| 8                   | NC                        |  |

| 9                   | NC                        |  |

| 10                  | NC                        |  |

| 11                  | NC                        |  |

| 12                  | NC                        |  |

| 13                  | NC                        |  |

| 14                  | NC                        |  |

| 15                  | NC                        |  |

| 16                  | NC                        |  |

| 17                  | NC                        |  |

| 18                  | GND                       |  |

| 19                  | NC                        |  |

| 20                  | NC                        |  |

| 21                  | NC                        |  |

| 22                  | NC                        |  |

| 23                  | NC                        |  |

| 32                  | NC                        |  |

| Table 3.6: M.2 E- | -Key Connector: M2_1 |

|-------------------|----------------------|

| 33                | GND                  |

| 34                | NC                   |

| 35                | PCIE_M2_z_TX4+       |

| 36                | NC                   |

| 37                | PCIE_M2_z_TX4-       |

| 38                | NC                   |

| 39                | GND                  |

| 40                | NC                   |

| 41                | PCIE_M2_RX4+         |

| 42                | NC                   |

| 43                | PCIE_M2_RX4-         |

| 44                | NC                   |

| 45                | GND                  |

| 46                | NC                   |

| 47                | CLK_M2E_z_PCIE+      |

| 48                | NC                   |

| 49                | CLK_M2E_z_PCIE-      |

| 50                | SUSCLK_z_EKEY        |

| 51                | GND                  |

| 52                | PLTRST_BUFFER#       |

| 53                | PCIE_a_CLKREQ2#      |

| 54                | BT_DISABLE#          |

| 55                | PCIE_WAKE#           |

| 56                | WIFI_DISABLE#        |

| 57                | GND                  |

| 58                | NC                   |

| 59                | NC                   |

| 60                | NC                   |

| 61                | NC                   |

| 62                | NC                   |

| 63                | GND                  |

| 64                | NC                   |

| 65                | NC                   |

| 66                | NC                   |

| 67                | NC                   |

| 68                | NC                   |

| 69                | GND                  |

| 70                | NC                   |

| 71                | NC                   |

| 72                | +V3.3SB_M.2_E        |

| 73                | NC                   |

| 74                | +V3.3SB_M.2_E        |

| 75                | GND                  |

| H1                | NC                   |

| H2                | NC                   |

| H3                | GND                  |

| H4                | GND                  |

#### 3.5.3 I2C Internal Connector: CN3

| Table 3.7: I2C Internal Connector: CN3 |                       |  |

|----------------------------------------|-----------------------|--|

| Pin                                    | Signal Pin Definition |  |

| 1                                      | GND                   |  |

| 2                                      | EC_I2C0_z_DAT         |  |

| 3                                      | EC_I2C0_z_CLK         |  |

| 4                                      | +V33_I2CCONN          |  |

## 3.5.4 RTC Battery Connector: BAT1

| Table 3.8: RTC battery Connector: BAT1 |                       |

|----------------------------------------|-----------------------|

| Pin                                    | Signal Pin Definition |

| 1                                      | +VBAT_b1              |

| 2                                      | GND                   |

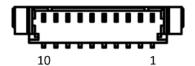

#### 3.5.5 COM-Port Internal Connector 1: COM1

| Table 3.9: COM-Port Internal Connector 1: COM1 |                       |

|------------------------------------------------|-----------------------|

| Pin                                            | Signal Pin Definition |

| 1                                              | NC                    |

| 2                                              | COM1_RI#              |

| 3                                              | COM1_DTR#             |

| 4                                              | COM1_CTS#             |

| 5                                              | COM1_TXD              |

| 6                                              | COM1_RTS#             |

| 7                                              | COM1_RXD              |

| 8                                              | COM1_DSR#             |

| 9                                              | COM1_DCD#             |

| 10                                             | GND                   |

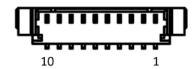

## 3.5.6 COM-Port Internal Connector 2: COM2

| Table 3.10: COM-Port Internal Connector 2: COM2 |                       |

|-------------------------------------------------|-----------------------|

| Pin                                             | Signal Pin Definition |

| 1                                               | NC                    |

| 2                                               | COM2_RI#              |

| 3                                               | COM2_DTR#             |

| 4                                               | COM2_CTS#             |

| 5                                               | COM2_TXD              |

| 6                                               | COM2_RTS#             |

| 7                                               | COM2_RXD              |

| 8                                               | COM2_DSR#             |

| 9                                               | COM2_DCD#             |

| 10                                              | GND                   |

#### 3.5.7 Front Panel Internal Connector: CN1

| Table 3.11: Front Panel Internal Connector: CN1 |                       |

|-------------------------------------------------|-----------------------|

| Pin                                             | Signal Pin Definition |

| 1                                               | GND                   |

| 2                                               | BUZZER-               |

| 3                                               | BUZZER+               |

| 4                                               | NC                    |

| 5                                               | SATA_HDD_LED#         |

| 6                                               | FP_a_PSIN#            |

| 7                                               | FP_a_RST#             |

| 8                                               | +V3.3                 |

| 9                                               | NC                    |

| 10                                              | +V5                   |

## 3.5.8 GPIO Internal Connector: CN2

| Table 3.12: GPIO Internal Connector: CN2 |                       |

|------------------------------------------|-----------------------|

| Pin                                      | Signal Pin Definition |

| 1                                        | GND                   |

| 2                                        | EC_P1_GPIO7           |

| 3                                        | EC_P1_GPIO2           |

| 4                                        | EC_P1_GPIO6           |

| 5                                        | EC_P1_GPIO1           |

| 6                                        | EC_P1_GPIO5           |

| 7                                        | EC_P1_GPIO0           |

| 8                                        | EC_P1_GPIO4           |

| 9                                        | +V5_P1_GPIO           |

| 10                                       | EC_P1_GPIO3           |

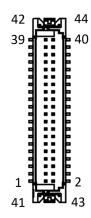

## 3.5.9 M.2 B-Key Connector: M2\_B1

| Table 3.13: M.2 B-I | Key Connector: M2_B1  |

|---------------------|-----------------------|

| Pin                 | Signal Pin Definition |

| 1                   | M2B1_CFG3             |

| 2                   | +V3.3A_M.2_B          |

| 3                   | GND                   |

| 4                   | +V3.3A_M.2_B          |

| 5                   | GND                   |

| 6                   | M2B1_FULL_CARD_OFF#   |

| 7                   | USB_M2B1_P            |

| 8                   | M2B1_W_DISABLE1#      |

| 9                   | USB_M2B1_N            |

| 10                  | M2B1_LED1#            |

| 11                  | GND                   |

| 20                  | M2B1_PCIE_DIS         |

| 21                  | M2B1_CFG0             |

| 22                  | M2B1_ANT_CFG          |

| 23                  | M2B1_WAKE_ON_WWAN#    |

| 24                  | M2B1_ANT_TUNER        |

| 25                  | M2B1_DPR              |

| 26                  | M2B1_W_DISABLE2#      |

| 27                  | GND                   |

| 28                  | NC                    |

| 29                  | M2B1_USB31_RX-        |

| 30                  | M2B1_UIM_RESET        |

| 31                  | M2B1_USB31_RX+        |

| 32                  | M2B1_UIM_CLK          |

| 33                  | GND                   |

| 34                  | M2B1_UIM_DATA         |

| 35                  | M2B1_USB31_TX-        |

| 36                  | M2B1_UIM_PWR          |

| 37                  | M2B1_USB31_TX+        |

| 38                  | NC                    |

| 39                  | GND                   |

| 40                  | NC                    |

| 41                  | MSATA_MPCIE_RX-       |

| 42                  | NC                    |

| 43                  | MSATA_MPCIE_RX+       |

| 44                  | NC                    |

| 45                  | GND                   |

| 46                  | NC                    |

| 47                  | MSATA_MPCIE_TX-       |

| 48                  | NC                    |

| 49                  | MSATA_MPCIE_TX+       |

| 50                  | M2B1_PERST#           |

| 51                  | GND                   |

| Table 2 12: M 2 B k | Key Connector: M2_B1 |

|---------------------|----------------------|

|                     | _                    |

| 52                  | M2B1_a_CLKREQ#       |

| 53                  | CLK100M_a_M2B1-      |

| 54                  | M2B1_PCIEWAKE#       |

| 55                  | CLK100M_a_M2B1+      |

| 56                  | NC                   |

| 57                  | GND                  |

| 58                  | NC                   |

| 59                  | NC                   |

| 60                  | NC                   |

| 61                  | NC                   |

| 62                  | NC                   |

| 63                  | NC                   |

| 64                  | NC                   |

| 65                  | NC                   |

| 66                  | NC                   |

| 67                  | M2B1_a_RESET#        |

| 68                  | M2B1_SUSCLK          |

| 69                  | M2B1_CFG1            |

| 70                  | +V3.3A_M.2_B         |

| 71                  | GND                  |

| 72                  | +V3.3A_M.2_B         |

| 73                  | GND                  |

| 74                  | +V3.3A_M.2_B         |

| 75                  | M2B1_CFG2            |

| H1                  | NC                   |

| H2                  | NC                   |

| H3                  | GND                  |

| H4                  | GND                  |

## 3.5.10 LVDS Connector: LVDS1

| <b>Table 3.14: L</b> | VDS Connector: LVDS1  |  |

|----------------------|-----------------------|--|

| Pin                  | Signal Pin Definition |  |

| 1                    | +V LCD                |  |

| 2                    | +V_LCD                |  |

| 3                    | GND                   |  |

| 4                    | GND                   |  |

| 5                    | +V_LCD                |  |

| 6                    | +V_LCD                |  |

| 7                    | LVDS1_0_D0-           |  |

| 8                    | LVDS1_1_D0-           |  |

| 9                    | LVDS1_0_D0+           |  |

| 10                   | LVDS1_1_D0+           |  |

| 11                   | GND                   |  |

| 12                   | GND                   |  |

| 13                   | LVDS1_0_D1-           |  |

| 14                   | LVDS1_1_D1-           |  |

| 15                   | LVDS1_0_D1+           |  |

| 16                   | LVDS1_1_D1+           |  |

| 17                   | GND                   |  |

| 18                   | GND                   |  |

| 19                   | LVDS1_0_D2-           |  |

| 20                   | LVDS1_1_D2-           |  |

| 21                   | LVDS1_0_D2+           |  |

| 22                   | LVDS1_1_D2+           |  |

| 23                   | GND                   |  |

| 24                   | GND                   |  |

| 25                   | LVDS1_0_CLK-          |  |

| 26                   | LVDS1_1_CLK-          |  |

| 27                   | LVDS1_0_CLK+          |  |

| 28                   | LVDS1_1_CLK+          |  |

| 29                   | GND                   |  |

| 30                   | GND                   |  |

| 31                   | LVDS0_DDCCLK_AUX+     |  |

| 32                   | LVDS0_DDCCLK_AUX-     |  |

| 33                   | GND                   |  |

| 34                   | GND                   |  |

| 35                   | LVDS1_0_D3-           |  |

| 36                   | LVDS1_1_D3-           |  |

| 37                   | LVDS1_0_D3+           |  |

| 38                   | LVDS1_1_D3+<br>NC     |  |

| 39<br>40             | LVDS1 VCON            |  |

| 41                   | NC                    |  |

| 42                   | NC<br>NC              |  |

| 42 43                | NC<br>NC              |  |

| 43                   | NC<br>NC              |  |

| 44                   | INC                   |  |

#### 3.5.11 Panel Inverter Connector: BL1

| Table 3.15: Panel Inverter Connector: BL1 |                       |

|-------------------------------------------|-----------------------|

| Pin                                       | Signal Pin Definition |

| 1                                         | +V5_1_INVERTER_0      |

| 2                                         | EC_LVDS1_z_PWM        |

| 3                                         | LVDS1_z_ENABKL        |

| 4                                         | GND                   |

| 5                                         | +V12_1_INVERTER_0     |

## 3.5.12 Panel Inverter Connector: POE\_PWR1

| Table 3.16: Panel Inverter Connector: POE_PWR1 |                       |

|------------------------------------------------|-----------------------|

| Pin                                            | Signal Pin Definition |

| 1                                              | +V48_LAN2+            |

| 2                                              | +V48_LAN2-            |

| 3                                              | GND                   |

| 4                                              | +V12_A                |

## 3.5.13 DC Power Input Connector (180D): CN4

| Table 3.17: DC Power Input Connector (180D): CN4 |                       |  |

|--------------------------------------------------|-----------------------|--|

| Pin                                              | Signal Pin Definition |  |

| 1                                                | +V12_DCIN             |  |

| 2                                                | GND                   |  |

## 3.5.14 DC Power Input Connector (90D): CN5

| Table 3.18: DC Power Input Connector (90D): CN5 |                       |  |

|-------------------------------------------------|-----------------------|--|

| Pin                                             | Signal Pin Definition |  |

| 1                                               | GND                   |  |

| 2                                               | +V12_DCIN             |  |

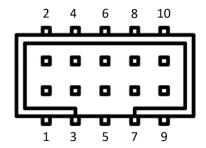

#### 3.5.15 USB 2.0 Dual-Port Internal Connector: USB1

| Table 3.19: USB 2.0 Dual-Port Internal Connector: USB1 |                       |  |

|--------------------------------------------------------|-----------------------|--|

| Pin                                                    | Signal Pin Definition |  |

| 1                                                      | +V5SB_USB_UTC         |  |

| 2                                                      | +V5SB_USB_UTC         |  |

| 3                                                      | USB6_z_P-             |  |

| 4                                                      | USB7_z_P-             |  |

| 5                                                      | USB6_z_P+             |  |

| 6                                                      | USB7_z_P+             |  |

| 7                                                      | GND                   |  |

| 8                                                      | GND                   |  |

| 9                                                      | GND                   |  |

| 10                                                     | NC                    |  |

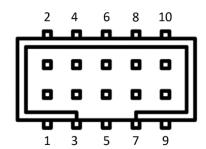

## 3.6 Audio Internal Connector: AUDIO1

| Table 3.20: Audio Internal Connector: AUDIO1 |                       |  |

|----------------------------------------------|-----------------------|--|

| Pin                                          | Signal Pin Definition |  |

| 1                                            | LOUTR                 |  |

| 2                                            | LINR                  |  |

| 3                                            | AUD_CONN_GND          |  |

| 4                                            | AUD_CONN_GND          |  |

| 5                                            | LOUTL                 |  |

| 6                                            | LINL                  |  |

| 7                                            | AUD_CONN_GND          |  |

| 8                                            | FRONT_JD              |  |

| 9                                            | MIC1R                 |  |

| 10                                           | MIC1L                 |  |

Chapter

4

AMI BIOS Setup

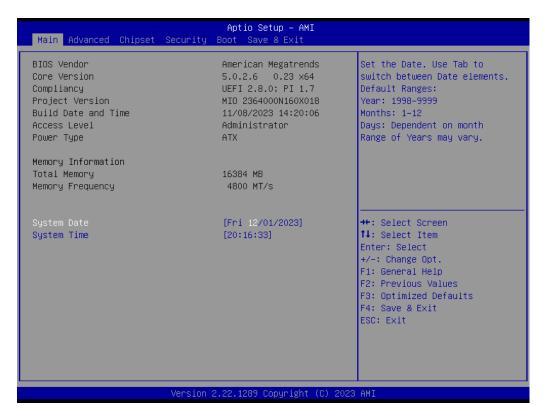

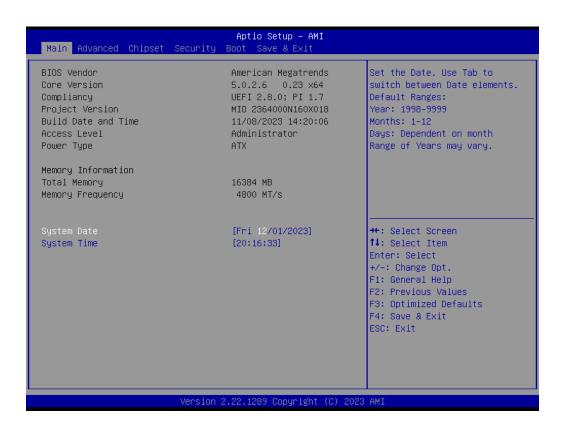

AMIBIOS has been integrated into many motherboards for over a decade. With the AMIBIOS Setup program, you can modify BIOS settings and control the various system features. This chapter describes the basic navigation of the MIO-2364 BIOS setup screens.

AMIBIOS ROM has a built-in setup program that allows users to modify the basic system configuration. This information is stored in battery-backed CMOS so it retains the setup information when the power is turned off.

# 4.1 Entering Setup

Turn on the computer and check for the patch code. If there is a number assigned to the patch code, it means that the BIOS supports your CPU. If there is no number assigned to the patch code, please contact an Advantech application engineer to obtain an up-to-date patch code file. This will ensure that your CPU's system status is valid. After ensuring that you have a number assigned to the patch code, press <DEL> and you will immediately be allowed to enter Setup.

## 4.1.1 Main Setup

When you first enter the BIOS Setup Utility, you will encounter the Main setup screen. You can always return to the Main setup screen by selecting the Main tab. There are two Main setup options. They are described in this section. The Main BIOS Setup screen is shown below.

The Main BIOS setup screen has two main frames. The left frame displays all the options that can be configured. Grayed-out options cannot be configured; options in blue can. The right frame displays the key legend.

Above the key legend is an area reserved for a text message. When an option is selected in the left frame, it is highlighted in white. Often a text message will accompany it.

#### System Time / System Date

Use this option to change the system time and date. Highlight System Time or System Date using the <Arrow> keys. Enter new values through the keyboard. Press the <Tab> key or the <Arrow> keys to move between fields. The date must be entered in MM/DD/YY format. The time must be entered in HH:MM:SS format.

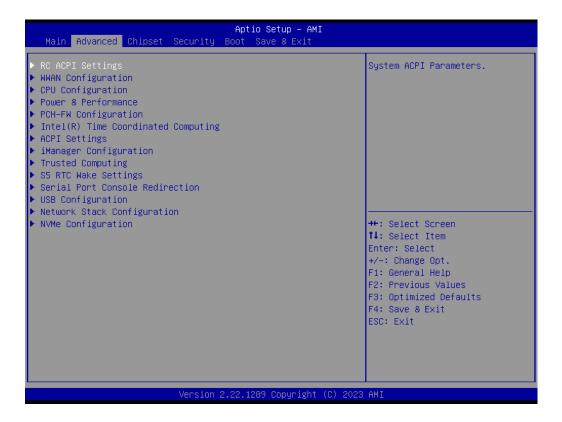

## 4.1.2 Advanced BIOS Features Setup

Select the Advanced tab from the MIO-2364 setup screen to enter the Advanced BIOS Setup screen. You can select any of the items in the left frame of the screen, such as CPU Configuration, to go to the sub-menu for that item. You can display an Advanced BIOS Setup option by highlighting it using the <Arrow> keys. All Advanced BIOS Setup options are described in this section. The Advanced BIOS Setup screen is shown below. The sub-menus are described on the following pages.

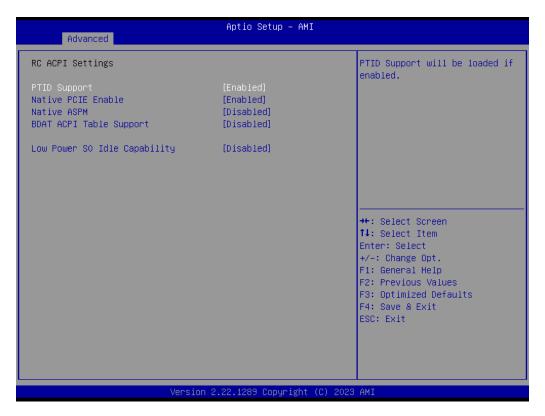

#### 4.1.2.1 RC ACPI Settings

#### **PTID Support**

Determines if it is enabled to load the PTID table.

#### **Native PCIE Enable**

Enable/Disable PCIE Native Control reported in the ACPI Table.

#### **Native ASPM**

Choose if the ASPM feature is controlled by the OS or BIOS.

#### **BDAT ACPI Table Support**

Determines if it is enabled to support BDAT ACPI Table.

#### Low Power S0 Idle Capability

Enable/Disable ACPI Low Power S0 Idle capability under the OS.

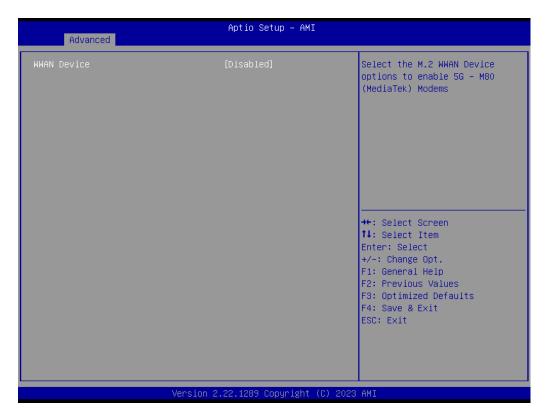

#### 4.1.2.2 WWAN Configuration

#### **WWAN Device**

Select the M.2 WWAN Device options to enable 5G-M80 (MediaTek) modems.

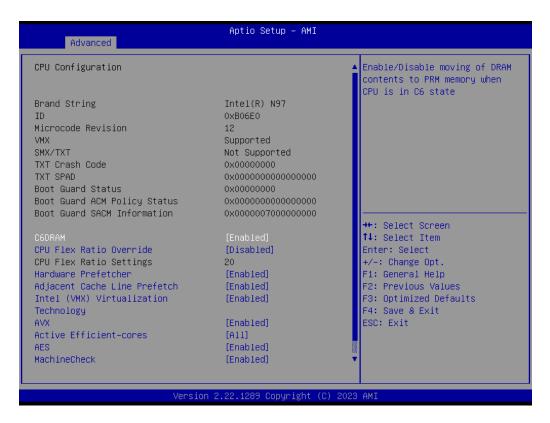

#### 4.1.2.3 CPU Configuration

#### **C6DRAM**

Enable/Disable the moving of DRAM contents to PRM memory when the CPU is in the C6 state.

#### **CPU Flex Ratio Override**

Enable/Disable CPU Flex Ratio Programming.

#### **Hardware Prefetcher**

This item allows users to enable or disable the hardware prefetcher feature.

#### **Adjacent Cache Line Prefetch**

This item allows users to enable or disable the adjacent cache line prefetch feature.

#### Intel (VMX) Virtualization Technology

When enabled, a VMM can utilize the additional hardware capability provided by Vanderpool Technology.

#### AVX

Enable/Disable the AVX 2/3 instructions.

#### **Active Efficient-cores**

Number of E-cores to enable in each processor package.

#### **AES**

Enable/Disable AES (Advanced Encryption Standard).

#### MachineCheck

Enable/Disable Machine Check.

#### **MonitorMWait**

Enable/Disable MonitorMWait.

#### **Intel Trusted Execution Technology**

Enables utilization of additional hardware capability provided by Intel® Trusted Execution Technology.

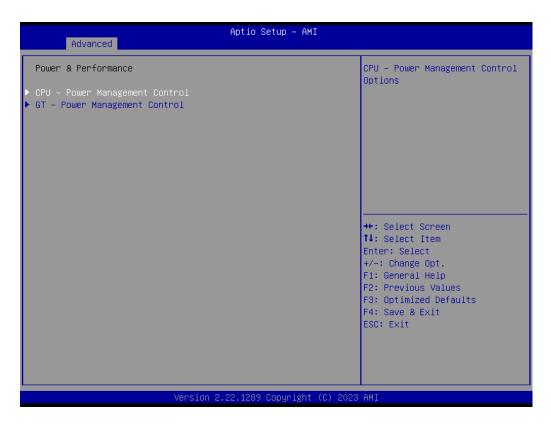

#### 4.1.2.4 Power & Performance

#### **CPU – Power Management Control**

CPU - Power Management Control options.

#### **GT – Power Management Control**

GT - Power Management Control options.

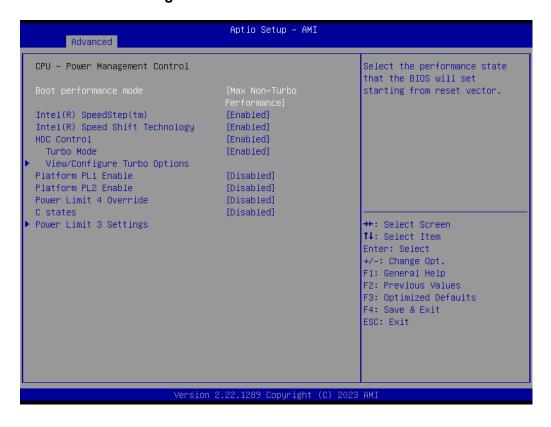

#### CPU - Power Management Control

Select the performance state that the BIOS will set before OS handoff.

#### Intel® SpeedStep®

Allows more than two frequency ranges to be supported.

#### Intel® Speed Shift Technology

Enable/Disable Intel® Speed Shift Technology support.

#### **HDC Control**

Enable/Disable Intel HDC.

#### **Turbo Mode**

Enable/Disable processor turbo mode.

#### **View/Configure Turbo Options**

View and Configure Turbo options.

#### **Platform PL1 Enable**

Enable/Disable Platform Power Limit 1 programming.

#### Platform PL2 Enable

Enable/Disable Platform Power Limit 1 programming.

#### **Power Limit 4 Override**

Enable/Disable Power Limit 4 override.

#### C states

Enable/Disable CPU Power Management.

#### **Power Limit 3 Settings**

Power Limit 3 settings.

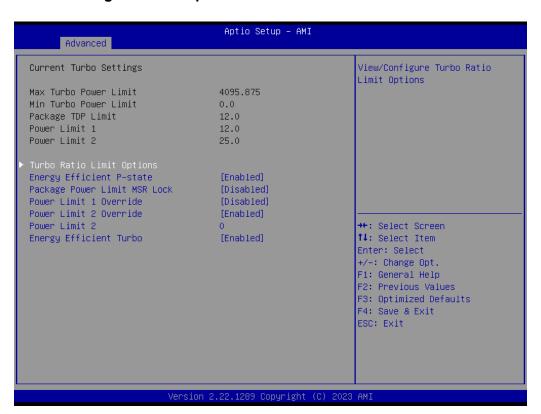

#### ■ View/Configure Turbo Options

#### **Turbo Ratio Limit Option**

View/Configure Turbo Ratio Limit options.

#### **Energy Efficient P-state**

Enable/Disable Energy Efficient P-state feature.

#### **Package Power Limit MSR Lock**

Enable/Disable locking of Package Power Limit settings.

#### **Power Limit 1 Override**

Enable/Disable Power Limit 1 override.

#### **Power Limit 2 Override**

Enable/Disable Power Limit 2 override.

#### **Power Limit 2**

Power Limit 2 value in milliwatts; BIOS will round to the nearest 1/8W when programming.

#### **Energy Efficient Turbo**

Enable/Disable the Energy Efficient Turbo feature.

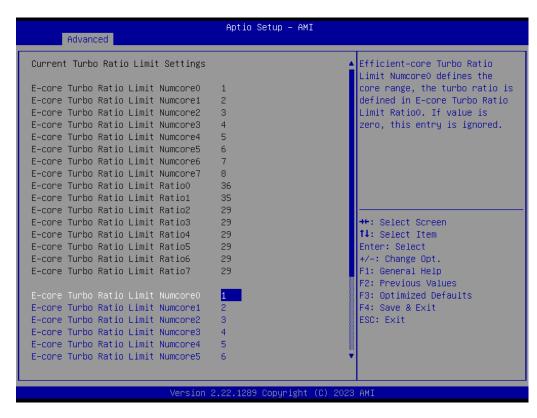

#### Config TDP Configurations

#### E-core Turbo Ratio Limit Numcore x

Efficient-core Turbo Ratio Limit Numcore x defines the core range.

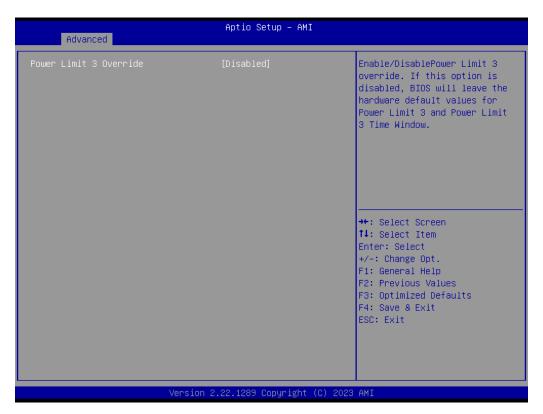

#### ■ Power Limit 3 Settings

#### **Power Limit 3 Override**

Enable/Disable Power Limit 3 override.

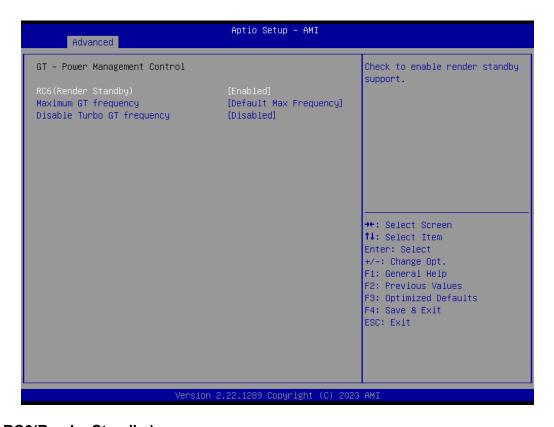

#### ■ GT - Power Management Control

#### RC6(Render Standby)

Check to enable render standby support.

#### **Maximum GT frequency**

Maximum GT frequency limited by user.

#### **Disable Turbo GT frequency**

Enabled/Disable Turbo GT frequency.

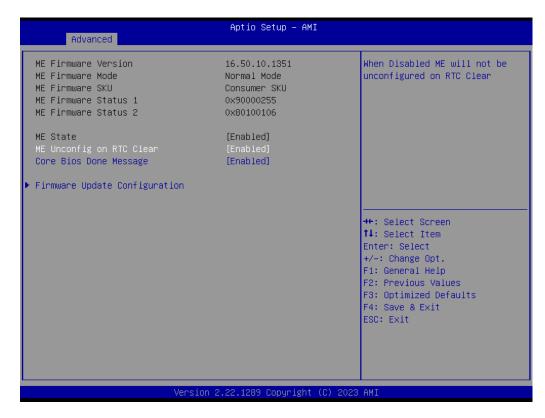

#### 4.1.2.5 PCH-FW Configuration

#### **ME State**

When disabled, ME will be put into Temporarily Disabled Mode.

#### **ME Unconfig on RTC Clear**

When disabled, ME will not be unconfigured on RTC Clear.

#### **Core BIOS Done Message**

Enable/Disable Core BIOS Done message sent to ME.

#### **Firmware Update Configuration**

Configure Management Engine Technology parameters.

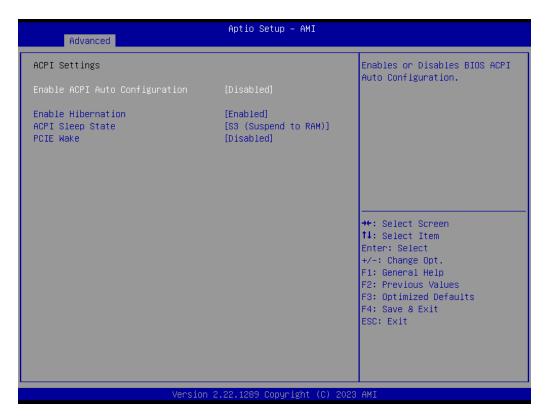

#### 4.1.2.6 ACPI Settings

#### **Enable ACPI Auto Configuration**

Enable/Disable BIOS ACPI auto configuration.

#### **Enable Hibernation**

Enable/Disable the ability to hibernate (OS/S4 Sleep State). This option may not be available with some OS.

#### **ACPI Sleep State**

Select the highest ACPI sleep state the system will enter when the SUSPEND button is pressed.

#### **PCIE Wake**

Enable/Disable PCIE to wake the system from S5.

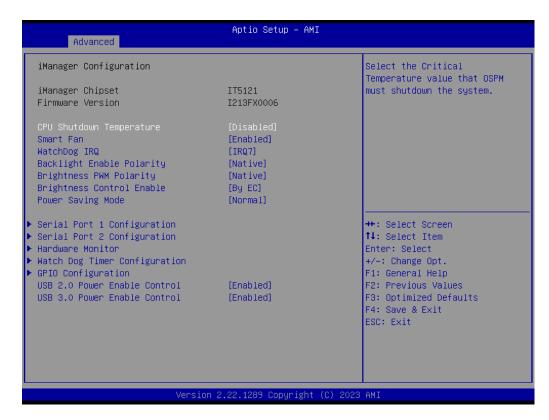

#### 4.1.2.7 iManager Configuration

#### **CPU Shutdown Temperature**

Select the Critical Temperature value at which OSPM must shut down the system.

#### **Smart Fan**

Control the iManager Smart Fan function.

#### Watchdog IRQ

Select IRQ Number eBrain WatchDog.

#### **Backlight Enable Polarity**

Switch Backlight Enable Polarity to Native or Invert.

#### **Brightness PWM Polarity**

Backlight Control Brightness PWM Polarity for Native or Invert.

#### **Brightness Control Enable**

Choose to control the LVDS brightness value by EC or User Override during the POST stage.

#### **Power Saving Mode**

Enable/Disable power saving mode.

#### **Serial Port 1 Configuration**

Set Parameters of Serial Port 1.

#### **Serial Port 2 Configuration**

Set Parameters of Serial Port 2.

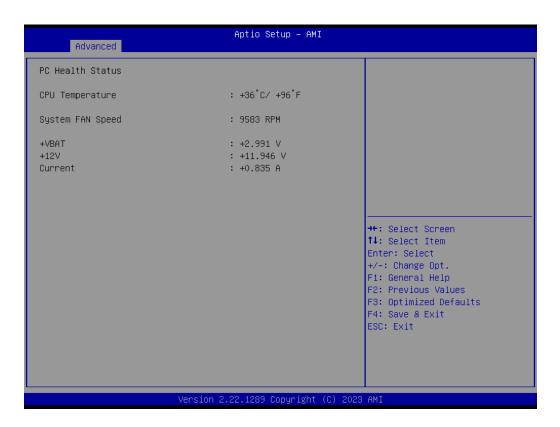

#### **Hardware Monitor**

Monitor hardware Status.

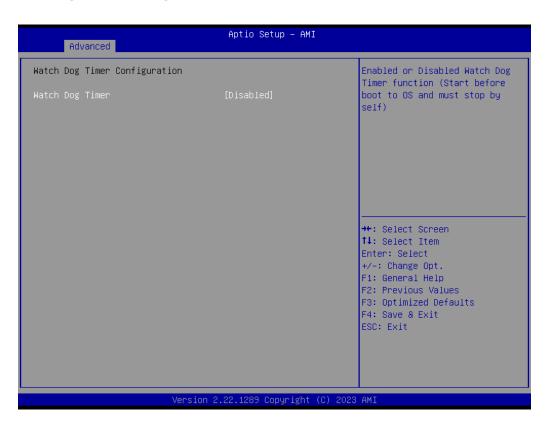

#### **Watch Dog Timer Configuration**

Watch Dog Timer Configuration Page.

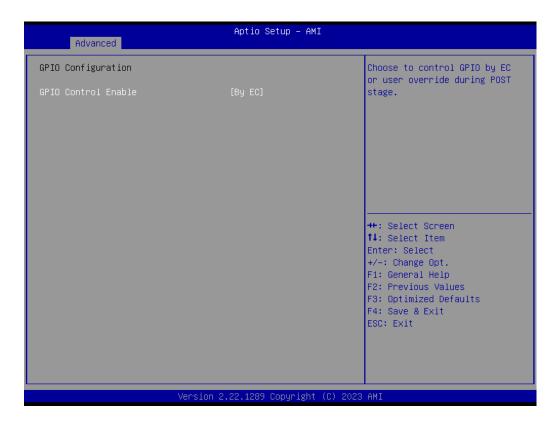

#### **GPIO Configuration**

**GPIO** Configuration Settings.

#### **USB 2.0 Power Enable Control**

Enable/Disable power off USB 2.0 port in S4/S5.

#### **USB 3.0 Power Enable Control**

Enable/Disable power off USB 3.0 port in S4/S5.

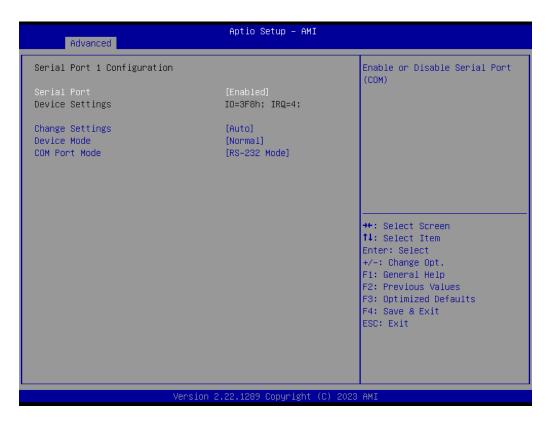

#### **Serial Port 1 Configuration**

#### **Serial Port**

Enable or disable Serial Port (COM).

#### **Change Settings**

Select optimal settings for a Super IO device.

#### **Device Mode**

If you use a baud rate above 115200, please select High Speed.

#### **COM Mode**

COM port mode select.

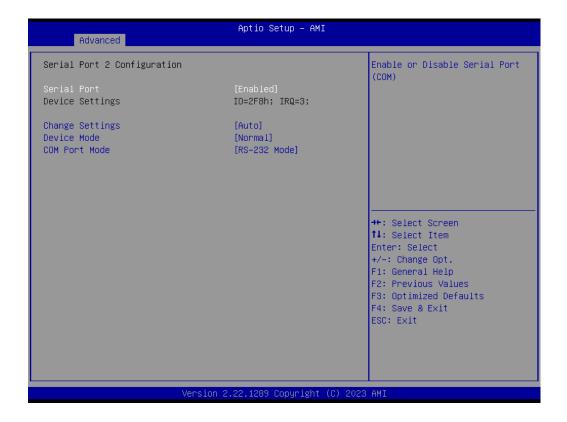

#### **Serial Port 2 Configuration**

#### **Serial Port**

Enable/Disable Serial Port (COM).

#### **Change Settings**

Select optimal settings for a Super IO device.

#### **Device Mode**

If you use a baud rate above 115200, please select High Speed.

#### **COM Mode**

COM port mode select.

#### **Hardware Monitor**

#### **Watch Dog Timer Configuration**

#### **Watch Dog Timer**

Enable/Disable the Watch Dog Timer Function.

#### **GPIO Configuration**

#### **GPIO Control Enable**

Choose to control GPIO by EC or User Override during the POST stage.

#### GPIO0/1/2/3/4/5/6/7

Configure GPIO0/1/2/3/4/5/6/7.

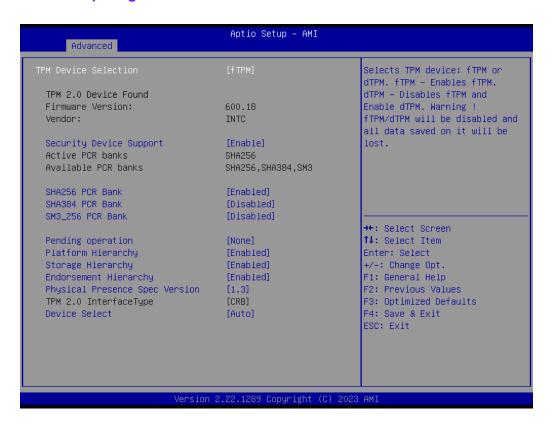

#### 4.1.2.8 Trusted Computing

#### **TPM Device Selection**

Select TPM device: fTPM or dTPM.

#### **Security Device Support**

Enable/Disable BIOS support for a security device.

#### SHA-1 PCR Bank

Enable/Disable SHA-1 PCR Bank.

#### SHA256 PCR Bank

Enable/Disable SHA256 PCR Bank.

#### SHA384 PCR Bank

Enable/Disable SHA384 PCR Bank.

#### **Pending operation**

Schedule an operation for the security device.

#### **Platform Hierarchy**

Enable/Disable Platform Hierarchy.

#### Storage Hierarchy

Enable/Disable Storage Hierarchy.

#### **Endorsement Hierarchy**

Enable/Disable Endorsement Hierarchy.

#### **TPM 2.0 UEFI Spec Version**

Select the TCG2 Spec Version support.

#### **Physical Presence Spec Version**

Select to instruct the OS to support PPI Spec Version 1.2 or 1.3.

#### **Device Select**

TPM 1.2 will restrict support to TPM 1.2 devices. TPM 2.0 will restrict support to TPM 2.0 devices.

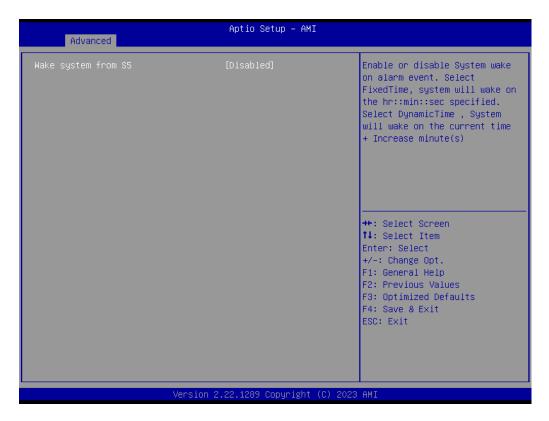

#### 4.1.2.9 S5 RTC Wake Settings

#### Wake system from S5

Enable/Disable system wake on alarm event. Select FixedTime for the system to wake on the hr:min:sec specified.

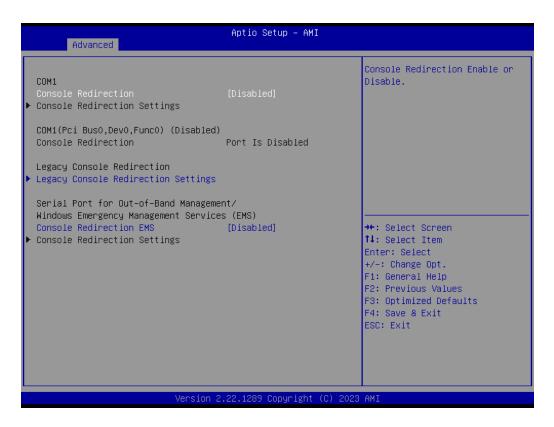

#### 4.1.2.10 Serial Port Console Redirection

#### **Console Redirection**

This item allows users to enable or disable console redirection for Microsoft Windows Emergency Management Services (EMS).

#### **Console Redirection**

This item allows users to configure console redirection detail settings.

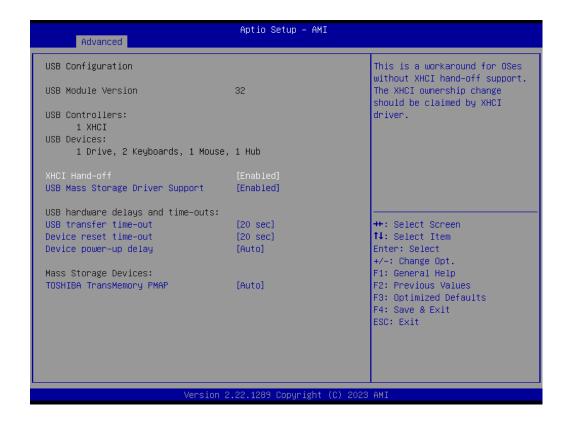

#### 4.1.2.11 USB Configuration

#### **XHCI Hand-off**

This is a workaround for OS without XHCI hand-off support. The XHCI ownership change should be claimed by the XHCI driver.

#### **USB Mass Storage Driver Support**

Enable/Disable USB mass storage driver support.

#### **USB** transfer time-out

Time-out value for control, bulk, and interrupt transfers.

#### Device reset time-out

USB mass storage device start unit command time-out.

#### Device power-up delay

Maximum time the device will take before it properly reports itself to the host controller. 'Auto' uses the default value: for a Root port it is 100 ms, for a Hub port the delay is taken from the Hub descriptor.

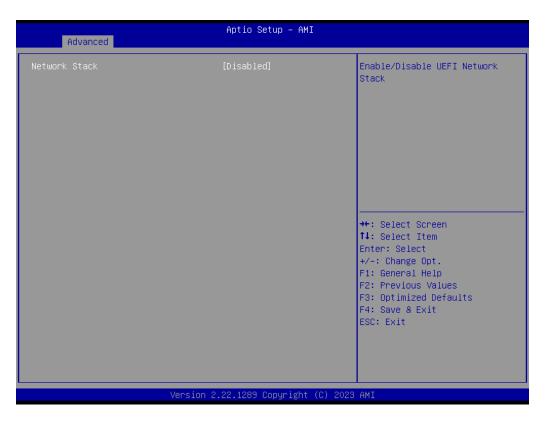

#### **Network Stack**

Enable/Disable UEFI Network Stack.

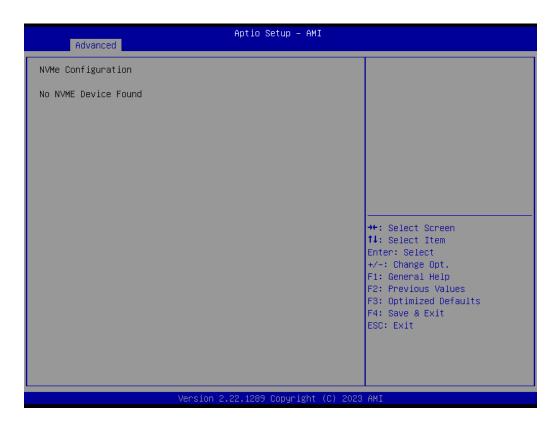

#### 4.1.2.13 NVMe Configuration

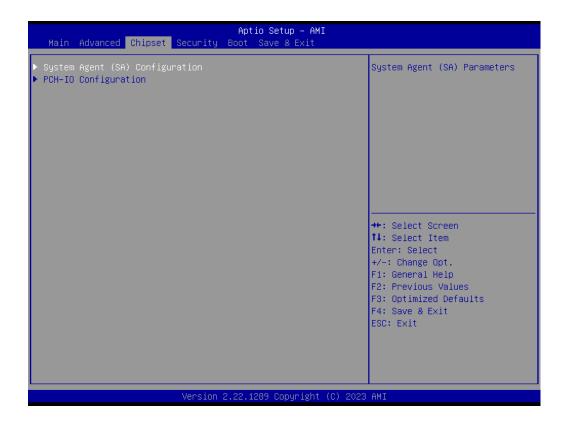

## 4.1.3 Chipset Configuration

Select the Chipset tab from the MIO-2364 setup screen to enter the Chipset BIOS Setup screen. You can display a Chipset BIOS Setup option by highlighting it using the <Arrow> keys. All Plug and Play BIOS Setup options are described in this section. The Plug and Play BIOS setup screen is shown below.

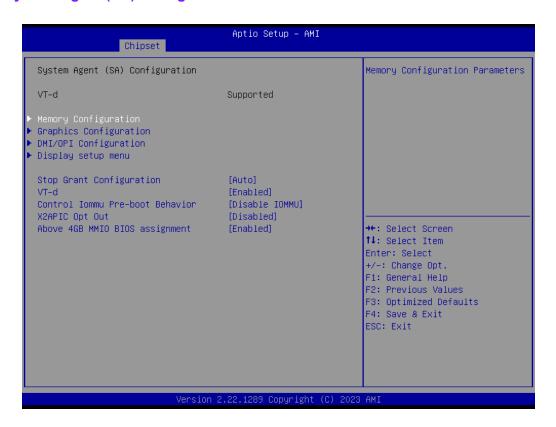

#### 4.1.3.1 System Agent (SA) Configuration

#### **Memory Configuration**

Memory configuration parameters.

#### **Graphics Configuration**

Graphics configuration parameters.

#### **DMI/OPI Configuration**

Control various DMI functions.

#### Display setup menu

Display configuration settings.

#### **Stop Grant Configuration**

Automatic/Manual stop grant configuration.

#### VT-d

VT-D capability.

#### **Control Iommu Pre-boot Behavior**

Enable IOMMU in Pre-boot environment.

#### **X2APIC Opt Out**

Enable/Disable X2APIC Opt Out Bit.

#### Above 4GB MMIO BIOS assignment

Enable/Disable above 4GB Memory Mapped IO BIOS assignment.

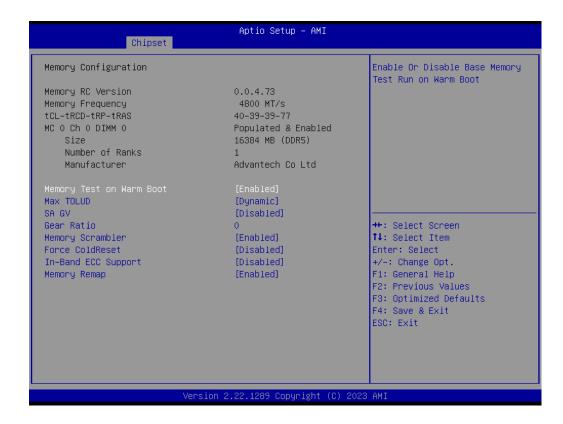

#### **Memory Configuration**

#### **Memory Test on Warm Boot**

Enable/Disable Base Memory Test Run on Warm Boot.

#### **Max TOLUD**

Maximum Value of TOLUD.

#### **SAGV**

System Agent Geyserville.

#### **Gear Ratio**

Gear ratio when SAGV is disabled.

#### **Memory Scrambler**

Enable/Disable Memory Scrambler support.

#### **Force ColdReset**

Force ColdReset OR Choose MrcColdBoot mode.

#### **In-Band ECC Support**

Enable/Disable In-Band ECC.

#### **Memory Remap**

Enable/Disable Memory Remap above 4GB.

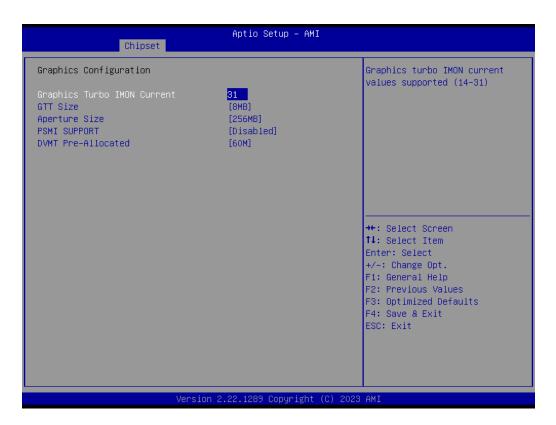

#### **Graphics Configuration**

#### **Graphics Turbo IMON Current**

Graphics turbo IMON current values supported.

#### **GTT Size**

Select the GTT Size.

#### **Aperture Size**

Select the Aperture Size.

#### **PSMI Support**

Enable/Disable PSMI.

#### **DVMT Pre-Allocated**

Select DVMT 5.0 Pre-Allocated (Fixed) Graphics Memory size used by the Internal Graphics Device.

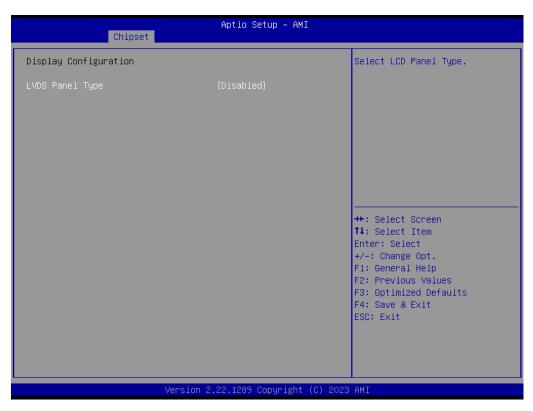

#### **LVDS**

#### **LVDS Panel Type**

This allows the user to select the LVDS panel resolution type.

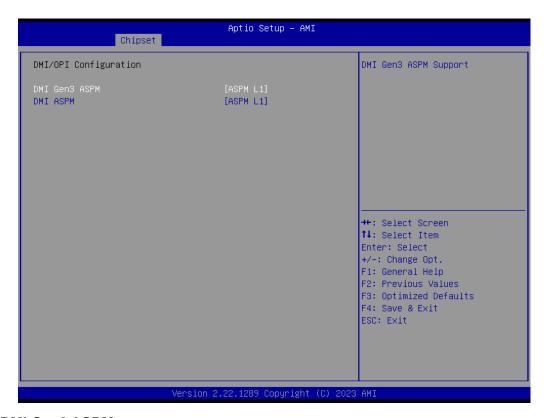

#### **DMI/OPI Configuration**

#### **DMI Gen3 ASPM**

DMI Gen3 ASPM Support.

#### **DMI ASPM**

DMI ASPM Support.

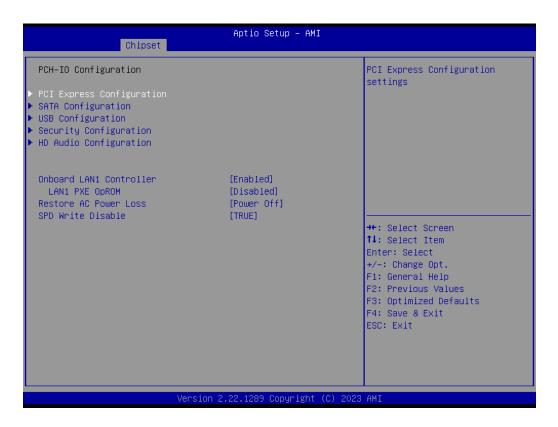

#### 4.1.3.2 PCH-IO Configuration

#### **PCI Express Configuration**

PCI Express configuration settings.

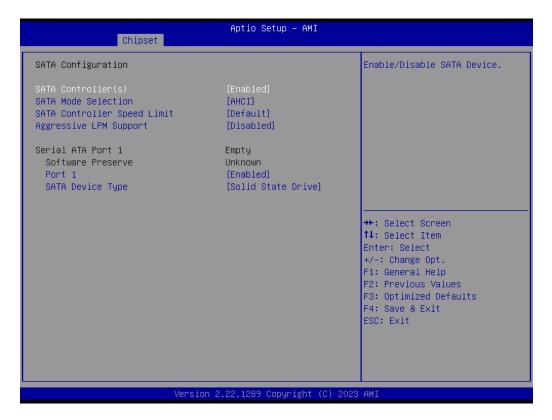

#### **SATA Configuration**

SATA device options settings.

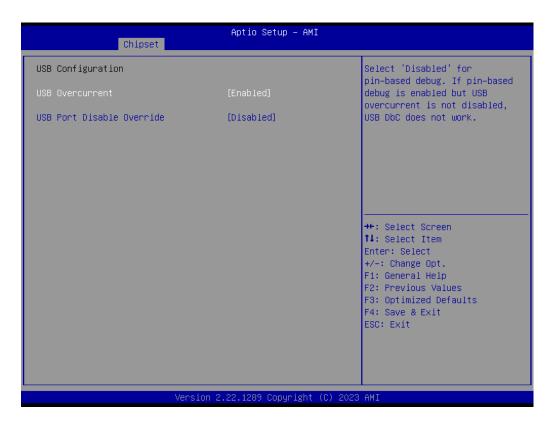

#### **USB** Configuration

USB configuration settings.

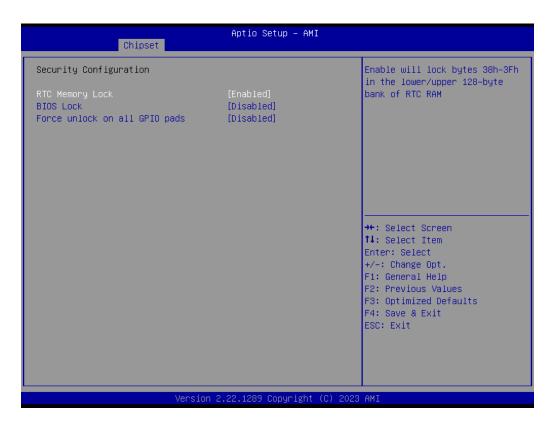

#### **Security Configuration**

Security configuration settings.

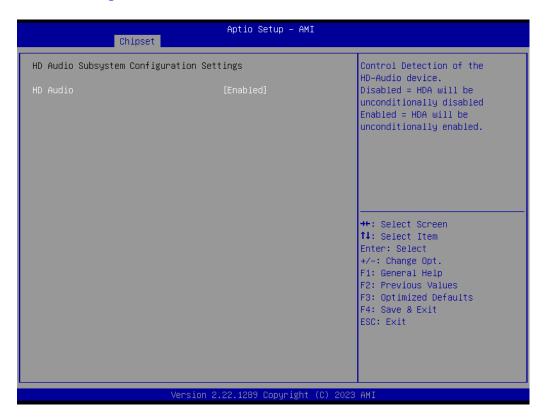

#### **HD Audio Configuration**

HD Audio subsystem configuration settings.

#### **Onboard LAN1 Controller**

Enable/Disable onboard LAN1 controller.

#### LAN1 PXE ROM

Enable/Disable onboard LAN1's PXE option ROM.

#### **Restore AC Power Loss**

Specify what state to go to when power is re-applied after a power failure (G3 state).

#### **SPD Write Disable**

Enable/Disable SPD Write Disable.

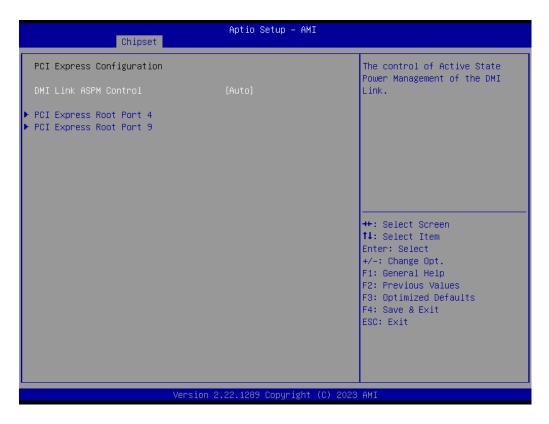

#### **PCI Express Configuration**

#### **DMI Link ASPM Control**

This item controls Active State Power Management of the DMI Link.

#### **PCI Express Root Port 4/9**

PCI Express Port 4/9 Settings.

#### **SATA Configuration**

#### SATA Controller(s)

Enable/Disable SATA device.

#### **SATA Mode Selection**

Determine how the SATA controller operates.

#### **SATA Controller Speed Limit**

Indicates the maximum speed the SATA controller can support.

#### **Aggressive LPM Support**

Enables PCH to aggressively enter link power state.

#### **USB** Configuration

#### **USB Overcurrent**

Select "Disabled" for pin-based debug.

#### **USB Port Disable Override**

Selectively Enable/Disable the corresponding USB Port from reporting a device connection to the controller.

### **Security Configuration**

#### **RTC Memory Lock**

Enable will lock bytes 38h-3Fh in the lower/upper 128-byte bank of RTC RAM.

#### **BIOS Lock**

Enable/Disable the PCH BIOS Lock Enable feature.

#### Force unlock on all GPIO pads

If Enabled, BIOS will force all GPIO pads to be in the unlock state.

#### **HD Audio Configuration**

#### **HD Audio**

Control detection of the HD-Audio device. Disabled = HDA will be unconditionally disabled. Enabled = HDA will be unconditionally enabled.

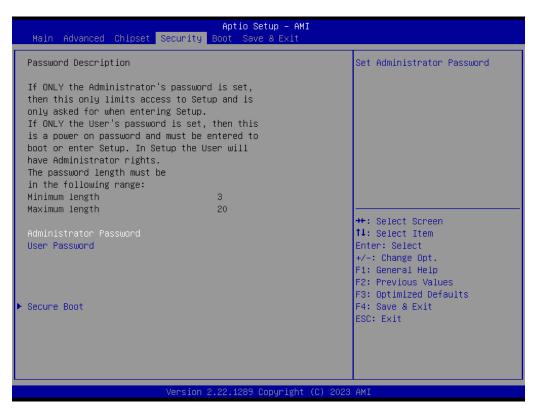

## 4.1.4 Security

Select security setup from the MIO-2364 setup main BIOS setup menu. All security setup options, such as password protection and virus protection are described in this section. To access the sub-menu for the following items, select the item and press <Enter>.

#### **Change Administrator / User Password**

Select this option and press <ENTER> to access the sub-menu, and then type in the password.

#### Secure Boot

Secure Boot Configurations.

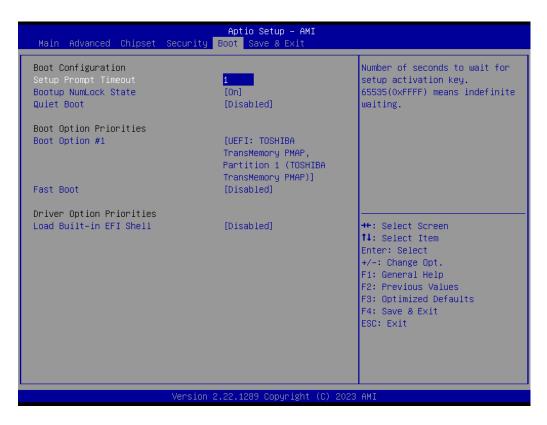

#### 4.1.5 **Boot**

#### **Setup Prompt Timeout**

This is the number of seconds that the firmware will wait before initiating the original default boot selection. A value of 0 indicates that the default boot selection is to be initiated immediately on boot. A value of 65535(0xFFFF) indicates that firmware will wait for user input before booting. This means the default boot selection is not automatically started by the firmware.

#### **Bootup NumLock State**

Select the keyboard NumLock state.

#### **Quiet Boot**

Enable/Disable the Quiet Boot option.

#### **Boot Option #1**

Sets the system boot order.

#### **Fast Boot**

Enable/Disable boot with initialization of a minimal set of devices required to launch the active boot option. It has no effect on BBS boot options.

#### Load Built-in EFI Shell

Load/Unload the internal built-in EFI shell image inside the BIOS. (The built-in EFI shell will still be loaded if no bootable device is found).

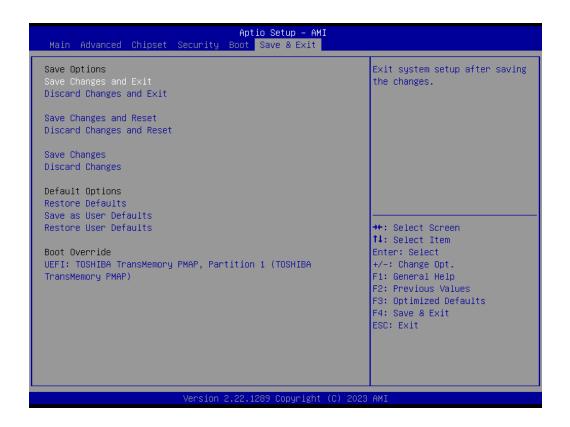

#### 4.1.6 Save & Exit

#### Save Changes and Exit

This item allows you to exit system setup after saving the changes.

#### **Discard Changes and Exit**

This item allows you to exit system setup without saving any changes.

#### Save Changes and Reset

This item allows you to reset the system after saving the changes.

#### **Discard Changes and Reset**

This item allows you to reset the system setup without saving any changes.

#### Save Changes

This item allows you to save changes done so far to any of the options.

#### **Discard Changes**

This item allows you to discard changes done so far to any of the options.

#### **Restore Defaults**

This item allows you to restore/load default values for all the options.

#### Save as User Defaults

This item allows you to save the changes done so far as user defaults.

#### **Restore User Defaults**

This item allows you to restore the user defaults to all the options.

#### **Boot Override**

Boot device select can override your boot priority.

# Appendix A

# **System Assignments**

This appendix contains information of a detailed nature.

Sections include:

- System I/O Ports

- 1st MB Memory Map

- Interrupt Assignments

# A.1 System I/O Ports

| Table A.1: System I/O Ports |                                                               |  |

|-----------------------------|---------------------------------------------------------------|--|

| Addr. Range (Hex)           | Device                                                        |  |

| 20h-2Dh                     | Programmable Interrupt Controller                             |  |

| 2Eh-2Fh                     | Motherboard Resources                                         |  |

| 30h-3Dh                     | Programmable Interrupt Controller                             |  |

| 40h-43h                     | System Timer/Counter                                          |  |

| 4Eh-4Fh                     | Motherboard Resources                                         |  |

| 50h-53h                     | System Timer/Counter                                          |  |

| 60h-6Fh                     | 8042 (keyboard controller) / NMI Controller / Microcontroller |  |

| 70h-7Fh                     | Real-Time Controller                                          |  |

| 80h-8Fh                     | Debug Port / Reserved                                         |  |

| 90h-9Fh                     | Debug Port / Reset Generator                                  |  |

| A0h-ADh                     | Programmable Interrupt Controller                             |  |

| B0h-B1h                     | Programmable Interrupt Controller                             |  |

| B4h-BDh                     | Power Management                                              |  |

| 29Ch-29Dh                   | Motherboard Resources                                         |  |

| 2F8h-2FFh                   | Communications Port (COM2)                                    |  |

| 3F8h-3FFh                   | Communications Port (COM1)                                    |  |

| 4D0h-4D1h                   | Programmable Interrupt Controller                             |  |

| 680h-69Fh                   | Motherboard Resources                                         |  |