# **User Manual**

## **AIMB-292**

Thin Al Motherboard with 12th/13th/14th Gen Intel® Core™ Processor and MXM GPU Integration

### Copyright

The documentation and the software included with this product are copyrighted 2025 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated, or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. The information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties that may result from its use.

### **Acknowledgments**

IBM and PC are trademarks of International Business Machines Corporation.

Intel® Core™ i9/i7/i5/i3, Pentium®, and Celeron® are trademarks of Intel Corporation.

All other product names or trademarks are properties of their respective owners.

### **Product Warranty (2 Years)**

Advantech warrants the original purchaser that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products that have been repaired or altered by persons other than repair personnel authorized by Advantech, or products that have been subject to misuse, abuse, accident, or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced free of charge during the warranty period. For out-of-warranty repairs, customers will be billed according to the cost of replacement materials, service time, and freight. Please consult your dealer for more details.

If you believe your product to be defective, follow the steps outlined below.

- Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages displayed when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- If your product is diagnosed as defective, obtain a return merchandise authorization (RMA) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a completed Repair and Replacement Order Card, and a proof of purchase date (such as a photocopy of your sales receipt) into a shippable container. Products returned without a proof of purchase date are not eligible for warranty service.

- 5. Write the RMA number clearly on the outside of the package and ship the package prepaid to your dealer.

Part No. 2006029201 Printed in China Edition 2 August 2025

### A Message to the Customer

#### **Advantech Customer Services**

Each and every Advantech product is built to the most exacting specifications to ensure reliable performance in the harsh and demanding conditions typical of industrial environments. Whether your new Advantech equipment is destined for the laboratory or the factory floor, you can be assured that your product will provide the reliability and ease of operation for which the name Advantech has come to be known. Your satisfaction is our primary concern. Here is a guide to Advantech's customer services. To ensure you get the full benefit of our services, please follow the instructions below carefully.

#### **Technical Support**

We want you to get the maximum performance from your products. If you run into technical difficulties, we are here to help. For the most frequently asked questions, you can easily find answers in your product documentation. These answers are normally a lot more detailed than the ones we can give over the phone.

Please consult this manual first. If you still cannot find the answer, gather all the information or questions that apply to your problem, and with the product close at hand, call your dealer. Our dealers are well trained and ready to give you the support you need to get the most from your Advantech products. In fact, most problems reported are minor and are able to be easily solved over the phone.

In addition, free technical support is available from Advantech engineers every business day. We are always ready to give advice on application requirements or specific information on the installation and operation of any of our products.

### **Declaration of Conformity**

#### **FCC Class B**

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for assistance.

## **CPU Compatibility**

| Processor Number      | Max TDP | Code Name             | Cores/Threads |

|-----------------------|---------|-----------------------|---------------|

| i9-14900              | 65W     | Raptor Lake-S Refresh | 8P+16E/32T    |

| i9-14900T             | 35W     | Raptor Lake-S Refresh | 8P+16E/32T    |

| i7-14700              | 65W     | Raptor Lake-S Refresh | 8P+12E/28T    |

| i7-14700T             | 35W     | Raptor Lake-S Refresh | 8P+12E/28T    |

| i5-14500              | 65W     | Raptor Lake-S Refresh | 6P+8E/20T     |

| i5-14500T             | 35W     | Raptor Lake-S Refresh | 6P+8E/20T     |

| i5-14400              | 65W     | Raptor Lake-S Refresh | 6P+4E/16T     |

| i5-14400T             | 35W     | Raptor Lake-S Refresh | 6P+4E/16T     |

| i3-14100              | 60W     | Raptor Lake-S Refresh | 4P+0E/8T      |

| i3-14100T             | 35W     | Raptor Lake-S Refresh | 4P+0E/8T      |

| Intel® Processor 300  | 46W     | Raptor Lake-S Refresh | 2P+0E/4T      |

| Intel® Processor 300T | 35W     | Raptor Lake-S Refresh | 2P+0E/4T      |

| i9-13900              | 65W     | Raptor Lake-S         | 8P+16E/32T    |

| i9-13900E             | 65W     | Raptor Lake-S         | 8P+16E/32T    |

| i9-13900TE            | 35W     | Raptor Lake-S         | 8P+16E/32T    |

| i7-13700              | 65W     | Raptor Lake-S         | 8P+8E/24T     |

| i7-13700E             | 65W     | Raptor Lake-S         | 8P+8E/24T     |

| i7-13700TE            | 35W     | Raptor Lake-S         | 8P+8E/24T     |

| i5-13500              | 65W     | Raptor Lake-S         | 6P+8E/20T     |

| i5-13500E             | 65W     | Raptor Lake-S         | 6P+8E/20T     |

| i5-13500TE            | 35W     | Raptor Lake-S         | 6P+8E/20T     |

| i5-13400              | 65W     | Raptor Lake-S         | 6P+4E/16T     |

| i5-13400E             | 65W     | Raptor Lake-S         | 6P+4E/16T     |

| i3-13100              | 60W     | Raptor Lake-S         | 4P+0E/8T      |

| i3-13100E             | 60W     | Raptor Lake-S         | 4P+0E/8T      |

| i3-13100TE            | 35W     | Raptor Lake-S         | 4P+0E/8T      |

| i9-12900              | 65W     | Alder Lake-S          | 8P+8E/24T     |

| i9-12900E             | 65W     | Alder Lake-S          | 8P+8E/24T     |

| i9-12900TE            | 35W     | Alder Lake-S          | 8P+8E/24T     |

| i7-12700              | 65W     | Alder Lake-S          | 4P+8E/20T     |

| i7-12700E             | 65W     | Alder Lake-S          | 8P+8E/24T     |

| i7-12700TE            | 35W     | Alder Lake-S          | 8P+8E/24T     |

| i5-12500              | 65W     | Alder Lake-S          | 6P+6E/12T     |

| i5-12500E             | 65W     | Alder Lake-S          | 6P+6E/12T     |

| i5-12500TE            | 35W     | Alder Lake-S          | 6P+6E/12T     |

| i5-12400              | 65W     | Alder Lake-S          | 6P+6E/12T     |

| i3-12100              | 60W     | Alder Lake-S          | 4P+4E/8T      |

| i3-12100E             | 60W     | Alder Lake-S          | 4P+4E/8T      |

| i3-12100TE            | 35W     | Alder Lake-S          | 4P+4E/8T      |

| G7400E                | 46W     | Alder Lake-S          | 2P+2E/4T      |

| G7400TE               | 35W     | Alder Lake-S          | 2P+2E/4T      |

| G6900E                | 46W     | Alder Lake-S          | 2P+2E/4T      |

| G6900TE               | 35W     | Alder Lake-S          | 2P+2E/2T      |

### **Memory Compatibility**

| Category | Speed | Capacity | Vendor    | ADVANTECH P/N      | ECC |

|----------|-------|----------|-----------|--------------------|-----|

| DDR5     | 5600  | 48GB     | ADVANTECH | SQR-SD5N48G5K6M    | N   |

| DDR5     | 5600  | 32GB     | ADVANTECH | SQR-SD5N32G5K6SNPB | N   |

### **Initial Inspection**

Before you begin installing your motherboard, please make sure that the following materials have been shipped:

- 1 x AIMB-292 Thin AI Motherboard

- 1 x SATA HDD cable

- 1 x SATA power cable

- 1 x Serial port cable

- 1 x I/O port bracket

- 1 x Startup Manual

- 1 x Warranty Card

- 2 x screws (M3x4.5L)

If any of these items are missing or damaged, contact your distributor or sales representative immediately. We have carefully inspected the AIMB-292 mechanically and electrically before shipment. It should be free of marks and scratches and in perfect working order upon receipt. As you unpack the AIMB-292, check it for signs of shipping damage. (For example, damaged box, scratches, dents, etc.) If it is damaged or it fails to meet the specifications, notify our service department or your local sales representative immediately. Also notify the carrier. Retain the shipping carton and packing material for inspection by the carrier. After inspection, we will make arrangements to repair or replace the unit.

# **Contents**

| Chapter | 1    | General Introduction                                    | .1   |

|---------|------|---------------------------------------------------------|------|

|         | 1.1  | Introduction                                            | 2    |

|         | 1.2  | Features                                                | 2    |

|         | 1.3  | Specifications                                          | 2    |

|         |      | 1.3.1 System                                            | 2    |

|         |      | 1.3.2 Memory                                            | 2    |

|         |      | 1.3.3 Input/Output                                      | 2    |

|         |      | 1.3.4 Graphics                                          | 3    |

|         |      | 1.3.5 Ethernet LAN                                      | 3    |

|         |      | 1.3.6 Industrial Features                               | 3    |

|         |      | 1.3.7 Mechanical and Environmental Specifications       | 3    |

|         | 1.4  | Jumpers and Connectors                                  | 4    |

|         |      | Table 1.1: I/O Connector                                | 4    |

|         |      | Table 1.2: Box Header                                   | 4    |

|         |      | Table 1.3: Pin Header                                   |      |

|         |      | Table 1.4: Jumper Settings                              |      |

|         | 1.5  | Board Layout: Jumper and Connector Locations            |      |

|         |      | Figure 1.1 Jumper and Connector Locations (Top Side)    |      |

|         |      | Figure 1.2 Jumper and Connector Locations (Bottom Side) |      |

|         | 1.6  | AIMB-292 Board Diagram                                  |      |

|         |      | Figure 1.3 AIMB-292 Board Diagram                       |      |

|         | 1.7  | Safety Precautions                                      |      |

|         | 1.8  | Jumper Settings                                         |      |

|         |      | 1.8.1 How to Set Jumpers                                |      |

|         |      | 1.8.2 Front Panel Header (JFP1)                         |      |

|         |      | Table 1.5: JFP1                                         |      |

|         |      | 1.8.3 CMOS Reset Header (JCMOS1)                        |      |

|         |      | Table 1.6: JCMOS1                                       |      |

|         |      | 1.8.4 AT/ATX Mode Selection (PSON1)                     |      |

|         |      | Table 1.7: PSON1                                        |      |

|         |      | 1.8.5 EDP Panel/LVDS Panel Voltage Selection (JLVDS1)   |      |

|         |      | Table 1.8: PSON1+JCMOS                                  |      |

|         | 1.9  | System Memory                                           |      |

|         | 1.10 | Memory Installation Procedures                          |      |

|         | 1.11 | Cache Memory                                            |      |

|         | 1.12 | Processor Installation                                  |      |

| Chapter |      |                                                         |      |

| Chapter | 2    | Connecting Peripherals                                  | 1 1  |

|         | 2.1  | Introduction                                            |      |

|         | 2.2  | I/O Connector                                           |      |

|         |      | 2.2.1 DC-In Connector (DCIN1)                           | . 12 |

|         |      | Table 2.1: DC-In Connector (DCIN1)                      | . 12 |

|         |      | 2.2.2 RJ-45 Dual LAN Ports (LAN1_LAN2)                  |      |

|         |      | Table 2.2: RJ-45 Dual LAN Ports (LAN1_LAN2)             |      |

|         |      | 2.2.3 RJ-45 Signal LAN Port (LAN3)                      |      |

|         |      | Table 2.3: RJ-45 Signal LAN Port (LAN3)                 | . 14 |

|         |      | 2.2.4 SATA (SATA1)                                      | . 14 |

|         |      | Table 2.4: SATA (SATA1)                                 |      |

|         |      | 2.2.5 SIM CARD (SIM1)                                   |      |

|         |      | Table 2.5: SIM CARD (SIM1)                              |      |

|         |      | 2.2.6 M.2 E-Key (M2_E1)                                 |      |

|         |      | Table 2.6: M.2 E-Key (M2_E1)                            | . 16 |

|         |      | 2.2.7 M.2 M-Key (M2_M1)                                 |      |

|         |      | /                                                       |      |

vii

|         |          |         | Table 2.7: M.2 E-Key (M2_M1)                                |            |

|---------|----------|---------|-------------------------------------------------------------|------------|

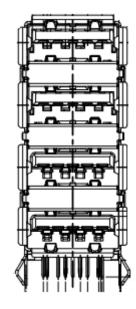

|         |          | 2.2.8   | MXM (MXM16-1)                                               |            |

|         |          | 2.2.9   | Audio (AUDIO1)                                              |            |

|         |          |         | Table 2.8: Audio (AUDIO1)                                   | . 18       |

|         |          | 2.2.10  | DisplayPort (DP1)                                           | . 19       |

|         |          |         | Table 2.9: DisplayPort (DP1)                                | . 19       |

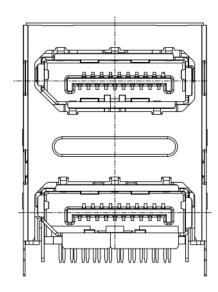

|         |          | 2.2.11  | Dual DisplayPort (DP2_DP3)                                  | . 20       |

|         |          |         | Table 2.10: Dual DisplayPort (DP2_DP3)                      | . 20       |

|         |          | 2.2.12  | USB Port 1234 (USB1234)                                     | . 21       |

|         |          |         | Table 2.11: USB Port 1234 (USB1234)                         |            |

|         | 2.3      | Box He  | eader                                                       | . 22       |

|         |          | 2.3.1   | COM1 Connector (COM1)                                       |            |

|         |          |         | Table 2.12: COM1 Connector (COM1)                           |            |

|         |          | 2.3.2   | COM2 Connector (COM2)                                       |            |

|         |          |         | Table 2.13: COM2 Connector (COM2)                           |            |

|         |          | 2.3.3   | EDP/LVDS Connector (EDP1_LVDS1)                             |            |

|         |          |         | Table 2.14: LVDS Pin Definitions                            |            |

|         |          |         | Table 2.15:eDP Pin Definitions                              |            |

|         |          | 2.3.4   | ATX 5V/PSON Connector (ATX_5VSB1)                           |            |

|         |          |         | Table 2.16:ATX 5V/PSON Connector (ATX_5VSB1)                |            |

|         |          | 2.3.5   | EDP/LVDS Backlight Inverter Power Connector (INV1)          |            |

|         |          | 2.0.0   | Table 2.17: EDP/LVDS Backlight Inverter Power Connector (IN |            |

|         |          |         | 25                                                          | ٠.,        |

|         |          | 2.3.6   | USB 56 (USB56)                                              | 26         |

|         |          | 2.0.0   | Table 2.18:USB 56 (USB56)                                   |            |

|         |          | 2.3.7   | SATA Power (SATA_PWR1)                                      |            |

|         |          | 2.0.7   | Table 2.19: SATA Power (SATA_PWR1)                          |            |

|         | 2.4      | Pin He  | ader                                                        |            |

|         | ∠.¬      | 2.4.1   | Power LED Pin Header (JFP2)                                 |            |

|         |          | ۷.٦.١   | Table 2.20: Power LED Pin Header (JFP2)                     |            |

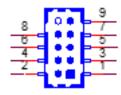

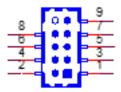

|         |          | 2.4.2   | General Purpose I/O Pin Header (GPIO1)                      |            |

|         |          | 2.7.2   | Table 2.21: General Purpose I/O Pin Header (GPIO1)          |            |

|         |          | 2.4.3   | CPUFAN (CPUFAN1)                                            |            |

|         |          | 2.4.0   | Table 2.22: CPUFAN (CPUFAN1)                                |            |

|         |          | 2.4.4   | SYSFAN (SYSFAN1)                                            |            |

|         |          | 2.7.7   | Table 2.23:SYSFAN (SYSFAN1)                                 |            |

|         |          | 2.4.5   | SYSFAN (SYSFAN2)                                            |            |

|         |          | 2.4.5   | Table 2.24:SYSFAN (SYSFAN2)                                 | 20         |

|         |          | 2.4.6   |                                                             |            |

|         |          | 2.4.0   | AMP (AMP 1)  Table 2.25: AMP (AMP 1)                        | 20         |

|         |          | 2.4.7   | Program VCORE Header (VR_PMB1)                              | . 20       |

|         |          | 2.4.7   | Table 2.26: Program VCORE Header (VR_PMB1)                  |            |

|         |          | 2.4.8   | MXM FAN (MXMFAN1)                                           |            |

|         |          | 2.4.0   | Table 2.27: MXM FAN (MXMFAN1)                               |            |

|         | 2.5      | lumno   | r Settings                                                  |            |

|         | 2.5      | 2.5.1   | Front Panel Header (JFP1)                                   |            |

|         |          | 2.3.1   | Table 2.28: Front Panel Header (JFP1)                       |            |

|         |          | 252     | ,                                                           |            |

|         |          | 2.5.2   | CMOS Reset Header (JCMOS1)                                  |            |

|         |          | 0.5.0   | Table 2.29: CMOS Reset Header (JCMOS1)                      |            |

|         |          | 2.5.3   | AT/ATX Mode Selection (PSON1)                               |            |

|         |          | 0.5.4   | Table 2.30:AT/ATX Mode Selection (PSON1)                    |            |

|         |          | 2.5.4   | EDP Panel / LVDS Panel Voltage Selection (JEDP1_LVDS1)      |            |

|         |          |         | Table 2.31: EDP Panel / LVDS Panel Voltage Selection (JEDP1 |            |

|         |          | 0.5.5   | VDS1)                                                       | . 30       |

|         |          | 2.5.5   | Program EC Header (JEC1)                                    | . 30       |

| Chapter | 3        | RIO     | S Operation                                                 | 21         |

| mapter  | <b>J</b> | סום     |                                                             | <i>)</i> 1 |

|         | 3.1      | Introdu | ction                                                       | . 32       |

|         |          |         |                                                             |            |

|         | 3.2 | BIO5 Setup                                                  | 3∠    |

|---------|-----|-------------------------------------------------------------|-------|

|         |     | Table 3.1: Control Keys                                     | 32    |

|         |     | 3.2.1 Main Menu                                             | 33    |

|         |     | 3.2.2 Advanced BIOS Features                                | 34    |

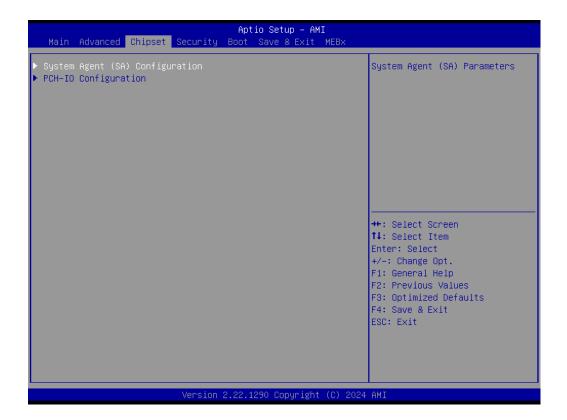

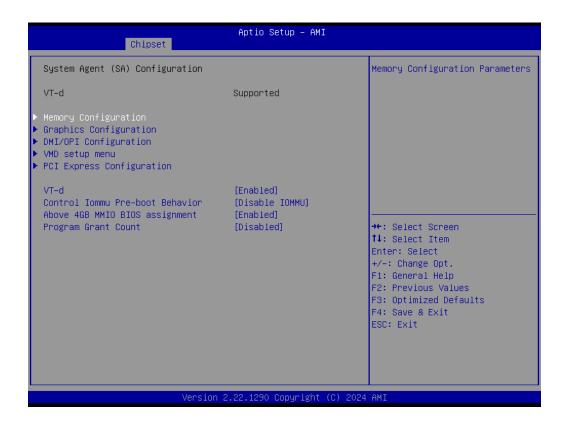

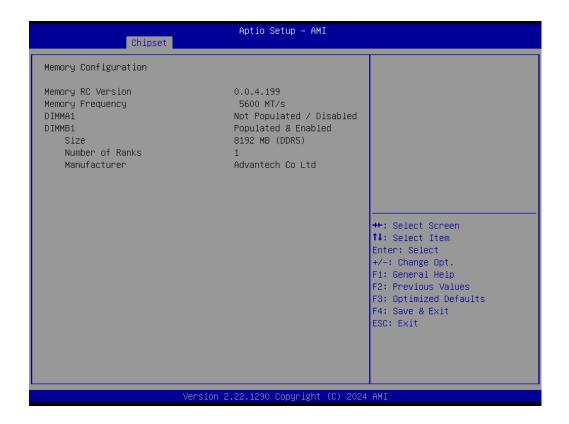

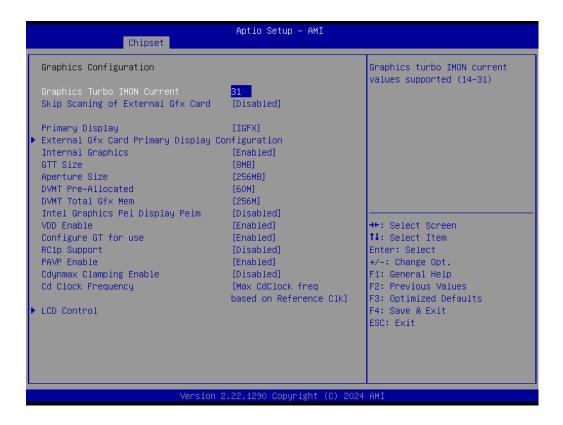

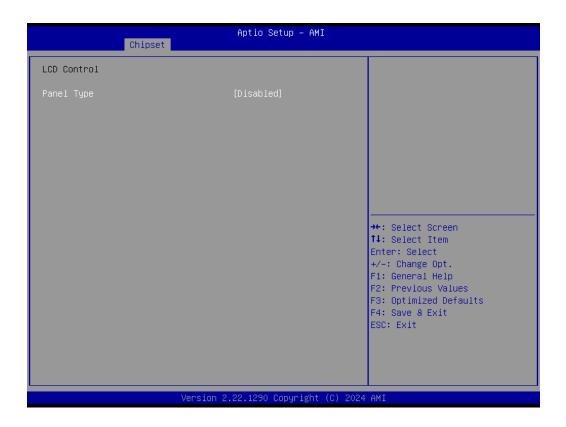

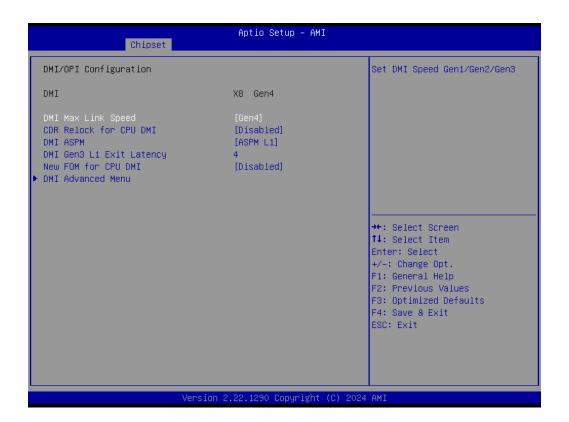

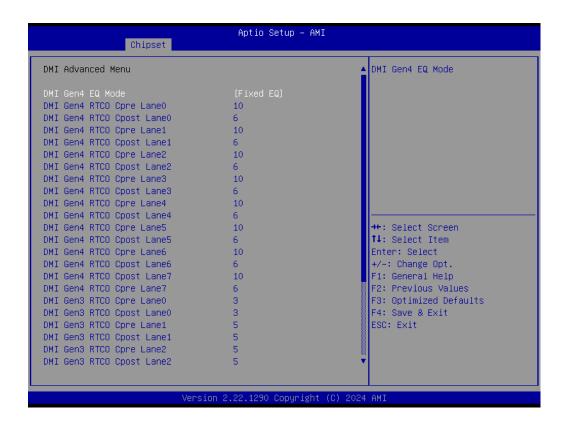

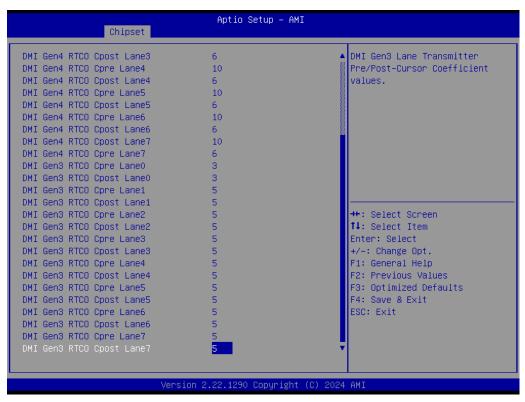

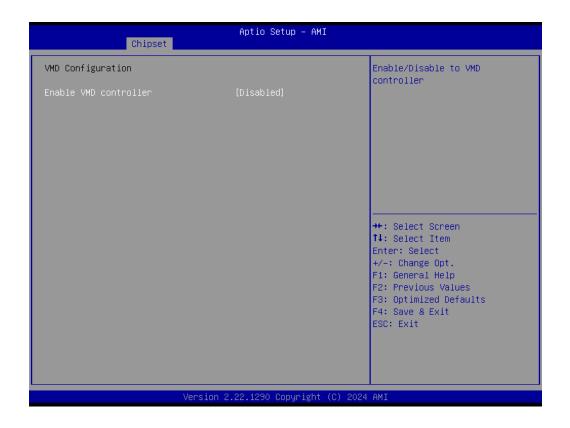

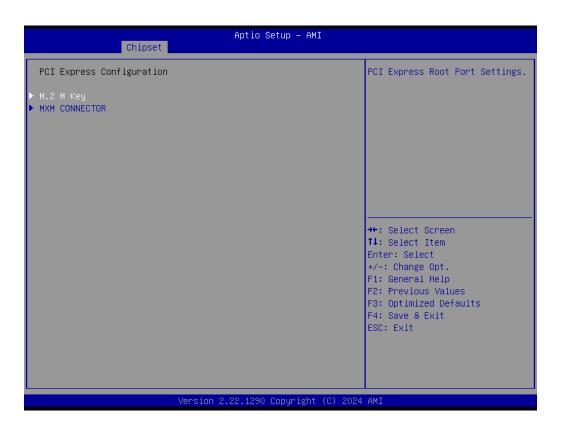

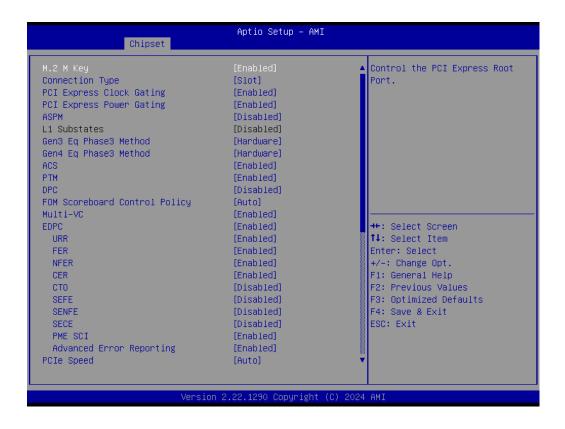

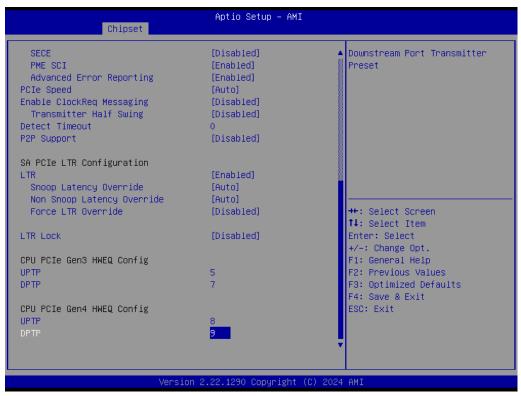

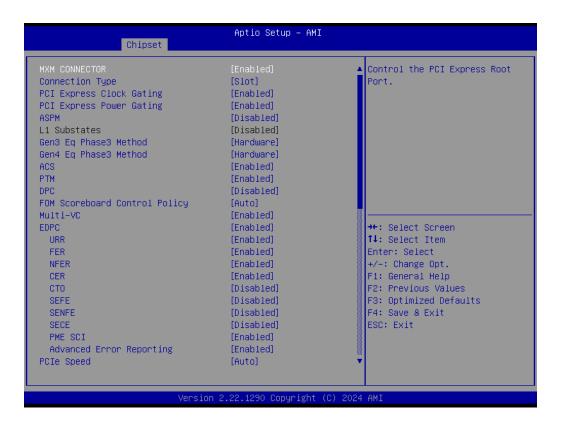

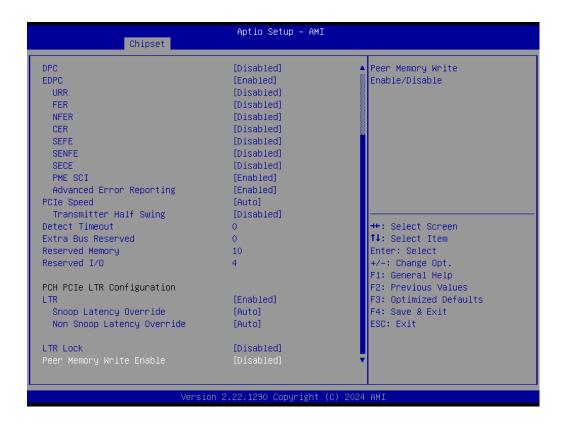

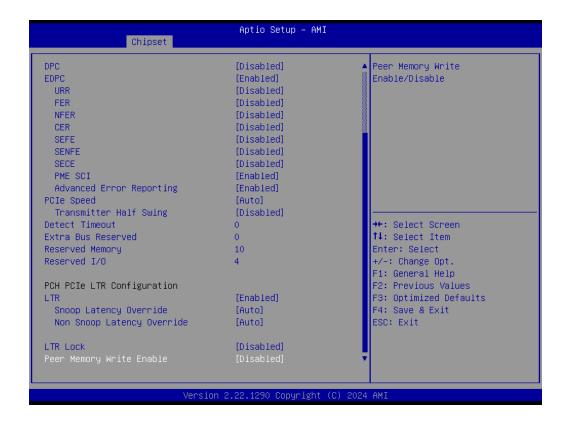

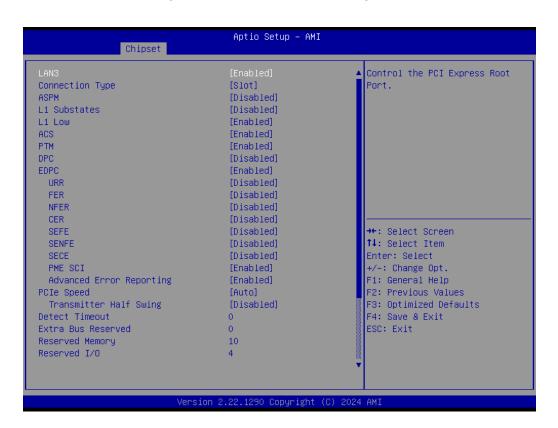

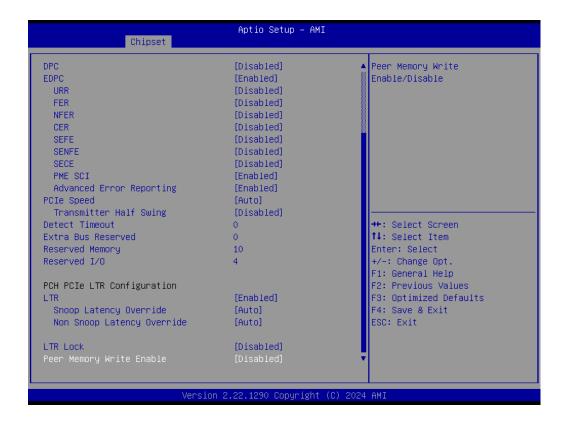

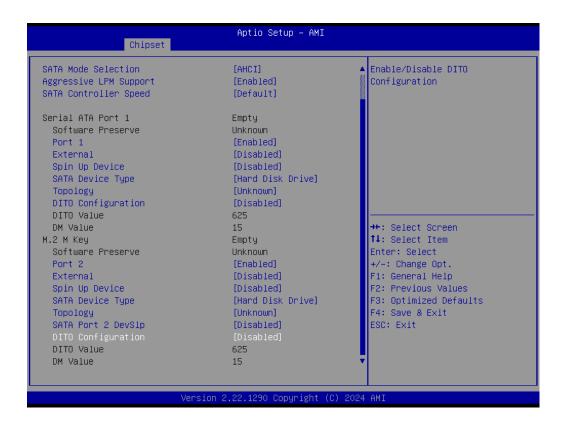

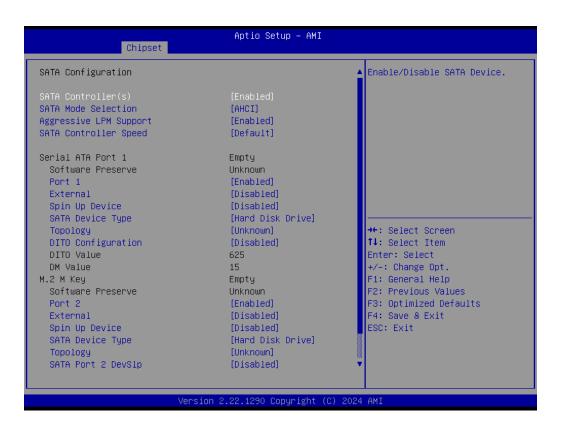

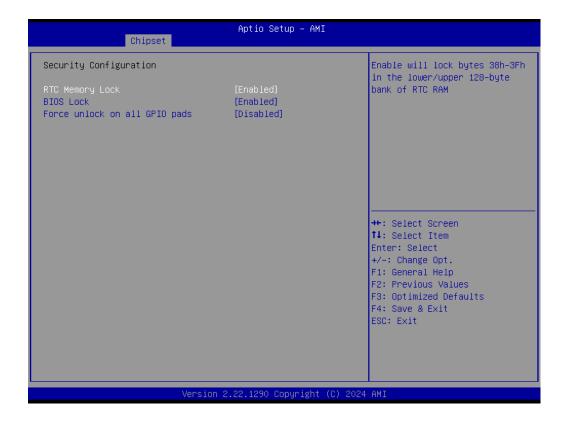

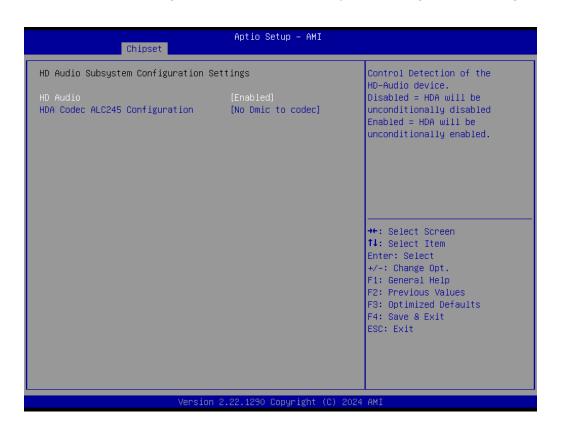

|         |     | 3.2.3 Chipset Configuration Setting                         |       |

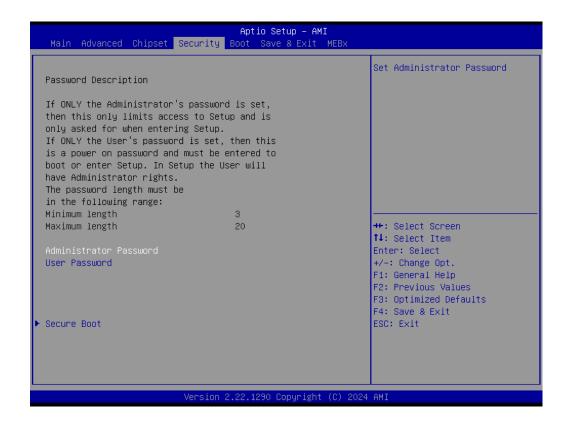

|         |     | 3.2.4 Security                                              |       |

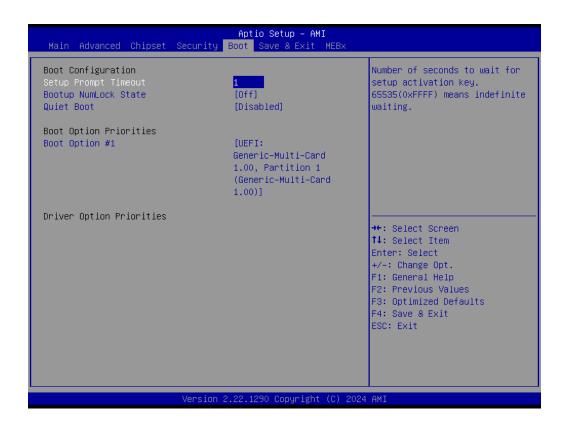

|         |     | 3.2.5 Boot Settings                                         |       |

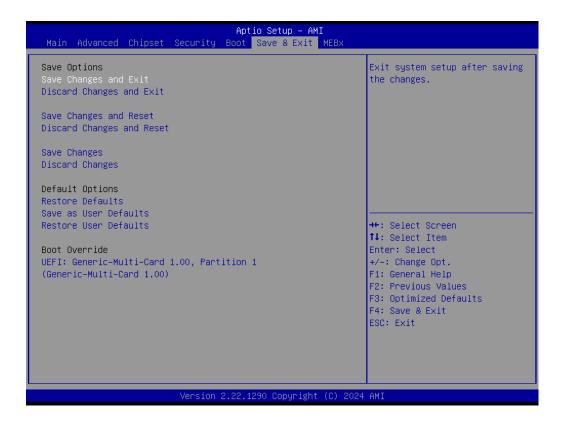

|         |     | 3.2.6 Save & Exit Configuration                             |       |

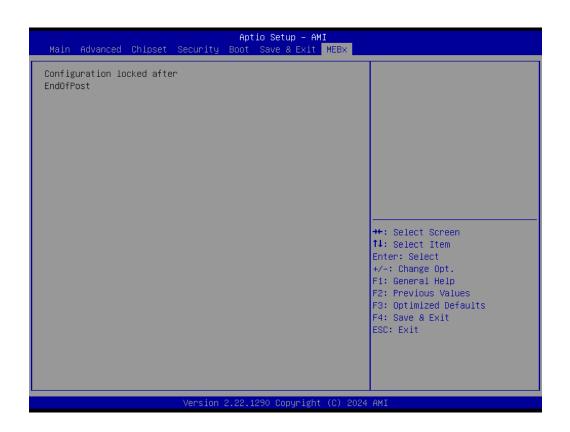

|         |     | 3.2.7 MEBx                                                  | 93    |

| Chapter | 4   | Software Introduction & Services.                           | 95    |

| Onapter | 7   | Software introduction & Services.                           |       |

|         | 4.1 | Introduction                                                | 96    |

|         | 4.2 | Value-Added Software Services                               |       |

|         |     | 4.2.1 Software API                                          |       |

|         |     | 4.2.2 Software Utility                                      | 98    |

| Chapter | 5   | Chipset Software Installation Utilit                        | ty 99 |

|         | 5.1 | Before You Begin                                            | 100   |

|         | 5.2 | Introduction                                                |       |

|         |     |                                                             |       |

| Chapter | 6   | LAN Configuration                                           | .101  |

|         | 6.1 | Introduction                                                | 102   |

|         | 6.2 | Features                                                    | 102   |

|         | 6.3 | Installation                                                |       |

|         | 6.4 | Windows® 10 Driver Setup (Intel® I226-V and Intel® I210-AT) | 102   |

# Chapter

**General Introduction**

### 1.1 Introduction

The AIMB-292 is engineered with the Intel® Q670E chipset, providing high performance and power efficiency for industrial applications. This motherboard supports Intel® Core™ i9/i7/i5/i3 LGA1700 CPUs up to 65W and dual-channel DDR5 5600MT/s SDRAM, with a maximum capacity of 96GB. It features a diverse range of I/O connectivity, including 2 serial ports, 4 USB 3.2 Gen2x1, 2 USB 2.0, 1 SATA III, and dual 2.5 GbE LAN ports along with 1 GbE LAN port. The AIMB-292 also offers flexible storage options with support for SATA HDDs, M.2 NVMe SSDs, and additional M.2 slots for Wi-Fi, Bluetooth, or LTE by option. This industrial motherboard is designed to accommodate NVIDIA RTX/Quadro GPUs, leveraging an ultra-slender design to deliver exceptional computing power and advanced graphics performance for visual computing and edge intelligence. It features both native Intel® UHD Graphics 770 and discrete NVIDIA Quadro® A4500 GPUs, with support for multiple display outputs including LVDS or eDP, and DP, offering maximum resolutions up to 4K.

### 1.2 Features

- I/O expansion: 2 serial ports, 4 USB 3.2 Gen2x1 and 2 USB 2.0, 1 SATA III, 1 M.2 M-Key & 1 M.2 E-Key (or 1 M.2 B-key by option), 2.5 GbE LAN and 1 GbE I AN

- Industrial motherboard featuring NVIDIA RTX/Quadro MXM GPU: The AIMB-292 leverages an ultra-slender design to deliver outstanding computing power and superior graphics performance for visual computing and edge intelligence.

- Wide selection of storage devices: SATA HDD, M.2 (M-Key and E-Key or B-Key by option). Customers benefit from the flexibility of using the most suitable storage device for the capacity needed.

### 1.3 Specifications

### **1.3.1** System

- **CPU**: Intel® Core™ i9/i7/i5/i3 LGA1700 CPU (up to 65W)

- BIOS: AMI EFI 256 Mbit SPI BIOS.

- System chipset: Intel® Q670E.

- SATA hard disk drive interface:

- One on-board SATA connector with a data transmission rate up to 6 GB/s

- One M.2 M-Key slot (2280), supporting NVMe SSD

- One M.2 E-Key slot (2230), supporting Wi-Fi/BT or One B-Key slot (3042), supporting LTE and storage by option

#### **1.3.2 Memory**

■ RAM: 2 x 262-pin SODIMM sockets support dual-channel DDR5 5600MT/s SDRAM, up to 96GB Max.

### 1.3.3 Input/Output

- **Serial ports:** 2 serial ports support RS-232/422/485 with auto flow control.

- USB port: Supports up to 4 USB 3.2 Gen2x1 and 2 USB 2.0

- **GPIO connector:** 8-bit general purpose Input/Output.

#### 1.3.4 Graphics

- Native GPU: Intel® UHD Graphics 770

- Discrete GPU: NVIDIA Quadro® A4500

- LVDS or eDP: 1 LVDS with maximum resolution up to 1920x1200 @ 60Hz or 1 eDP with maximum resolution up to 1920x1080 @ 60Hz by pass mode.

- **DP:** 2 DP 1.4a from MXM Type-A/B/B+ module, maximum resolution up to 4K at 120Hz and 1 x DP ++ from CPU maximum resolution up to 4096 x 2160 @ 60 Hz

#### 1.3.5 Ethernet LAN

- Supports three 10/100/1000/2500 Mbps Ethernet ports

- Controller:

GbE LAN1: Intel i226-VGbE LAN2: Intel i226-VGbE LAN3: Intel i210-AT

#### 1.3.6 Industrial Features

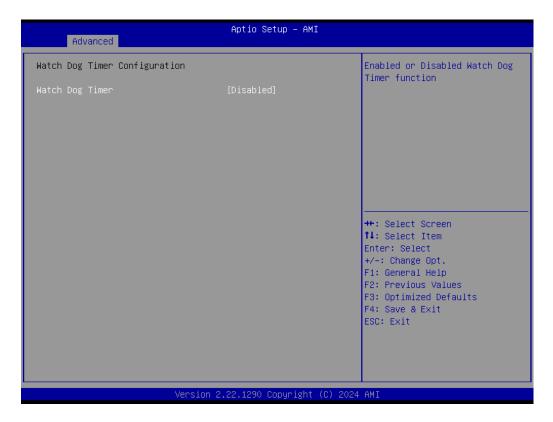

■ Watchdog timer: The watchdog timer can generate a system reset. It is programmable, with each unit equal to one second or one minute (255 levels).

### 1.3.7 Mechanical and Environmental Specifications

- Operating temperature: 0 ~ 55°C (32 ~ 131°F), depends on CPU speed and cooler solution

- Storage temperature: -40 ~ 85°C (-40 ~ 185°F).

- **Humidity:** 5 ~ 95% non-condensing.

- Power supply voltage: 24V

- Power consumption: Boost 100.2W; Typical 62.5W (configuration: Intel® Core™ i9-14900 5.4 GHz, 2pcs 48 GB DDR5 5600MHz SODIMM)

- Board size: 170 x 230 mm (6.69" x 9.06").

- Board weight: 1.5 kg

## 1.4 Jumpers and Connectors

Connectors on the AIMB-292 motherboard link it to devices such as hard disk drives and a keyboard. In addition, the board has a number of jumpers used to configure the system for your application.

The tables below list the function of each of the board jumpers and connectors. Later sections in this chapter give instructions on setting jumpers. Chapter 2 gives instructions for connecting external devices to your motherboard.

| Table 1.1: I/O Connector |                       |                |  |

|--------------------------|-----------------------|----------------|--|

|                          | Description           | Part Reference |  |

| 1                        | DC IN Connector       | DCIN1          |  |

| 2                        | RJ-45 Dual LAN ports  | LAN1_LAN2      |  |

| 3                        | RJ-45 Signal LAN port | LAN3           |  |

| 4                        | SATA                  | SATA1          |  |

| 5                        | SIM CARD              | SIM1           |  |

| 6                        | M.2 E-Key             | M2_E1          |  |

| 7                        | M.2 M-Key             | M2_M1          |  |

| 8                        | MXM                   | MXM16-1        |  |

| 9                        | Audio                 | AUDIO1         |  |

| 10                       | DisplayPort           | DP1            |  |

| 11                       | Dual DisplayPort      | DP2_DP3        |  |

| 12                       | USB Port 1234         | USB1234        |  |

| Table 1.2: Box Header |                                             |                |  |

|-----------------------|---------------------------------------------|----------------|--|

|                       | Description                                 | Part Reference |  |

| 1                     | COM1 Connector                              | COM1           |  |

| 2                     | COM2 Connector                              | COM2           |  |

| 3                     | EDP/LVDS Connector                          | EDP1_LVDS1     |  |

| 4                     | ATX 5V/PSON Connector                       | ATX_5VSB1      |  |

| 5                     | EDP/LVDS Backlight Inverter Power Connector | INV1           |  |

| 6                     | USB 56                                      | USB56          |  |

| 7                     | SATA Power                                  | SATA_PWR1      |  |

| Part Reference |

|----------------|

|                |

| JFP2           |

| GPIO1          |

| CPUFAN1        |

| SYSFAN1        |

| SYSFAN2        |

| AMP1           |

| VR_PMB1        |

| MXMFAN1        |

|                |

| Table 1.4: Jumper Settings |                                        |                |  |

|----------------------------|----------------------------------------|----------------|--|

|                            | Description                            | Part Reference |  |

| 1                          | Front Panel Header                     | JFP1           |  |

| 2                          | CMOS Reset Header                      | JCMOS1         |  |

| 3                          | AT/ATX Mode Selection                  | PSON1          |  |

| 4                          | EDP Panel/LVDS Panel Voltage Selection | JLVDS1         |  |

| 5                          | Program EC Header                      | JEC1           |  |

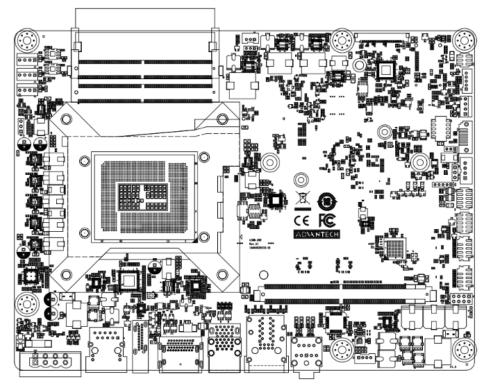

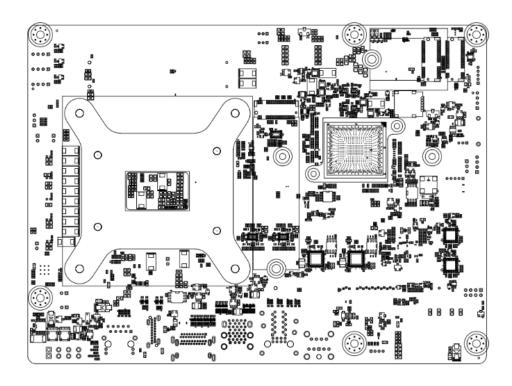

# 1.5 Board Layout: Jumper and Connector Locations

Figure 1.1 Jumper and Connector Locations (Top Side)

Figure 1.2 Jumper and Connector Locations (Bottom Side)

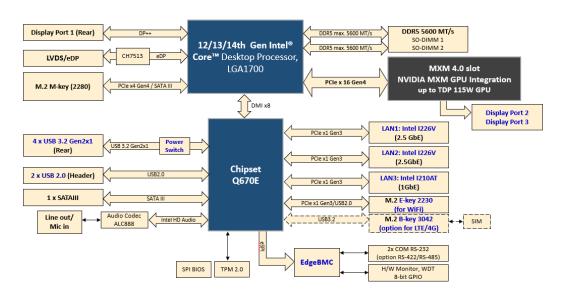

## 1.6 AIMB-292 Board Diagram

Figure 1.3 AIMB-292 Board Diagram

### 1.7 Safety Precautions

Warning! Always completely disconnect the power cord from the chassis whenever you work with the hardware. Do not make connections while the power is on. Sensitive electronic components can be damaged by sudden power surges. Only experienced electronics personnel should open the PC chassis.

Caution! Always ground yourself to remove any static charge before touching the motherboard. Modern electronic devices are very sensitive to electrostatic discharges. As a safety precaution, use a grounding wrist strap at all times. Place all electronic components on a static-dissipative surface or in a static-shielded bag when they are not in the chassis.

Caution! The computer is provided with a battery-powered real-time clock circuit. There is a danger of explosion if the battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

Caution! There is danger of a new battery exploding if it is incorrectly installed. Do not attempt to recharge, force open, or heat the battery. Replace the battery only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

#### 1.8 **Jumper Settings**

This section provides instructions on how to configure your motherboard by setting the jumpers. It also includes the motherboard's default settings and your options for each jumper.

#### 1.8.1 How to Set Jumpers

You can configure your motherboard to match the needs of your application by setting the jumpers. A jumper is a metal bridge that closes an electrical circuit. It consists of two metal pins and a small metal clip (often protected by a plastic cover) that slides over the pins to connect them. To "close" (or turn ON) a jumper, you connect the pins with the clip. To "open" (or turn OFF) a jumper, you remove the clip. Sometimes a jumper consists of a set of three pins, labeled 1, 2, and 3. In this case you connect either pins 1 and 2, or 2 and 3. A pair of needle-nose pliers may be useful when setting jumpers.

### 1.8.2 Front Panel Header (JFP1)

### Table 1.5: JFP1

| Pin | Signal         | Pin | Signal        |

|-----|----------------|-----|---------------|

| 1   | 3.3V           | 2   | FP_PANSWIN#   |

| 3   | FP_HDD_LED#    | 4   | GND           |

| 5   | SMB_DAT_RESUME | 6   | FP_SYS_RESET# |

| 7   | SMB_CLK_RESUME | 8   | GND           |

### 1.8.3 CMOS Reset Header (JCMOS1)

| Table 1.6: JCMOS1                |                 |

|----------------------------------|-----------------|

| Function                         | Jumper Settings |

| 1-2 (Default)<br>Keep CMOS data* | 1 2 3           |

| 2~3<br>Clear CMOS data           | 1 2 3           |

### 1.8.4 AT/ATX Mode Selection (PSON1)

| Table 1.7: PSON1          |                 |  |

|---------------------------|-----------------|--|

| Function                  | Jumper Settings |  |

| 1-2<br>AT Mode            | 1 2 3           |  |

| 2-3 (Default)<br>ATX Mode | 1 2 3           |  |

### 1.8.5 EDP Panel/LVDS Panel Voltage Selection (JLVDS1)

| Table 1.8: PSON1+JCMOS             |                |

|------------------------------------|----------------|

| Function                           | Jumper Setting |

| Jumper position for 3.3V (Default) | 2 4 6          |

| Jumper position for 5V             | 2 4 6          |

| Jumper position for 12V            | 2 4 6          |

### 1.9 System Memory

The AIMB-292 has two sockets for a 262-pin DDR5 SODIMM. These sockets use a 1.2 V unbuffered double data rate synchronous DRAM (DDR SDRAM). DRAM is available in capacities of 8GB, 16GB, 32GB and 48GB. The sockets can take any combination with SODIMMs of any size, giving a total memory size between 8GB, 16GB, 64GB, up to max 96GB. The AIMB-292 does NOT support error checking and correction (ECC).

### 1.10 Memory Installation Procedures

To install SODIMMs, first make sure the two handles of the SODIMM socket are in the "open" position, i.e., the handles lean outward. Slowly slide the SODIMM module along the plastic guides on both ends of the socket. Then firmly but gently (avoid pushing down too hard) press the SODIMM module well down into the socket, until you hear a click when the two handles have automatically locked the memory module into the correct position of the SODIMM socket. To remove the memory module, just push both handles outward, and the memory module will be ejected by the mechanism.

### 1.11 Cache Memory

The AIMB-292 supports a CPU with one of the following built-in full-speed last-level caches:

36MB for Intel® Core™-i9-14900/i9-14900T/i9-13900E/i9-13900TE

33MB for Intel® Core™-i7-14700/i7-14700T

30MB for Intel® Core™ i9-12900E/i9-12900TE

25MB for Intel® Core™ i7-12700E/i7-12700TE

24MB for Intel® Core™ i5-14500/ i5-14500T

20MB for Intel® Core™ i5-14400/ i5-14400T

18MB for Intel® Core™ i5-12500E/i7-12500TE

12MB for Intel® Core™ i3-14100/ i3-14100T/i3-12100E/i7-12100TE

6MB Intel® Pentium® Processor 300/ Intel® Processor 300T/G7400E/G7400TE

4MB Intel® Pentium® G6900E/G6900TE

The built-in second-level cache in the processor yields much higher performance than conventional external cache memory.

#### 1.12 Processor Installation

The AIMB-292 is designed to support 14th Gen Intel® Core™ i9/i7/i5/i3, Pentium®, and Celeron® LGA 1700 processors.

# Chapter

Connecting Peripherals

### 2.1 Introduction

You can access most of the connectors from the top of the board as it is being installed in the chassis. If you have a number of cards installed or have a packed chassis, you may need to partially remove the card to make all the connections.

### 2.2 I/O Connector

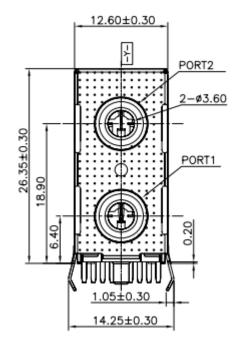

### 2.2.1 DC-In Connector (DCIN1)

| <b>Table 2.1: </b> [ | DC-In Connector (DCIN1 |  |

|----------------------|------------------------|--|

| Pin                  | Signal                 |  |

| 1                    | GND                    |  |

| 2                    | POWER                  |  |

| 3                    | POWER                  |  |

| 4                    | GND                    |  |

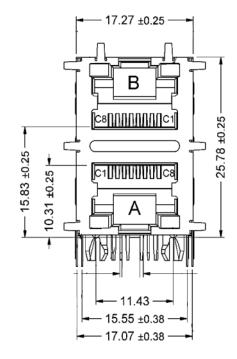

### 2.2.2 RJ-45 Dual LAN Ports (LAN1\_LAN2)

| Table 2 | 2.2: RJ-45 Dual LAN Ports (L | AN1_LA | N2)             |

|---------|------------------------------|--------|-----------------|

| Pin     | Signal                       | Pin    | Signal          |

| AL1     | LAN1_LED2_ACT#               | BL1    | LAN2_LED2_ACT#  |

| AL2     | +V3.3LAN1                    | BL2    | +V3.3LAN1       |

| AL3     | LAN1_LED1_2.5G#              | BL3    | LAN2_LED1_2.5G# |

| AL4     | LAN1_LED1_1G#                | BL4    | LAN2_LED1_1G#   |

| RA9     | GND                          | RB9    | GND             |

| RA1     | LAN1_MDI0+                   | RB1    | LAN2_MDI0+      |

| RA2     | LAN1_MDI0-                   | RB2    | LAN2_MDI0-      |

| RA3     | LAN1_MDI1+                   | RB3    | LAN2_MDI1+      |

| RA4     | LAN1_MDI1-                   | RB4    | LAN2_MDI1-      |

| RA5     | LAN1_MDI2+                   | RB5    | LAN2_MDI2+      |

| RA6     | LAN1_MDI2-                   | RB6    | LAN2_MDI2-      |

| RA7     | LAN1_MDI3+                   | RB7    | LAN2_MDI3+      |

| RA8     | LAN1_MDI3-                   | RB8    | LAN2_MDI3-      |

| RA10    | GND                          | RB10   | GND             |

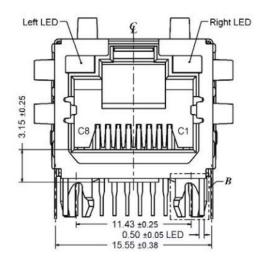

### 2.2.3 RJ-45 Signal LAN Port (LAN3)

| <b>Table</b> | 2.3: RJ-45 Signal LAN Port ( | LAN3) |            |

|--------------|------------------------------|-------|------------|

| Pin          | Signal                       | Pin   | Signal     |

| L1           | LAN3_LED1                    | L2    | +V3.3_LAN3 |

| L3           | LAN3_LED2                    | L4    | LAN3_LED0  |

| R5           | GND                          | R4    | LAN3_MDI1- |

| R1           | LAN3_MDI0+                   | R7    | LAN3_MDI2+ |

| R2           | LAN3_MDI0-                   | R8    | LAN3_MDI2- |

| R3           | LAN3_MDI1+                   | R9    | LAN3_MDI3+ |

| R10          | LAN3_MDI3-                   | R6    | GND        |

### 2.2.4 **SATA (SATA1)**

| <b>Table 2.4: S</b> | ATA (SATA1) |  |

|---------------------|-------------|--|

| Pin                 | Signal      |  |

| 1                   | GND         |  |

| 2                   | TX+         |  |

| 3                   | TX-         |  |

| 4                   | GND         |  |

| 5                   | RX-         |  |

| 6                   | RX+         |  |

| 7                   | GND         |  |

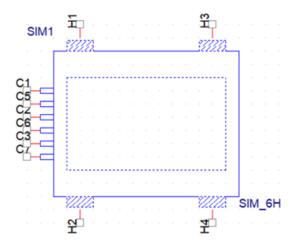

### 2.2.5 **SIM CARD (SIM1)**

| Table 2 | 2.5: SIM CARD (SIM1) |     |        |

|---------|----------------------|-----|--------|

| Pin     | Signal               | Pin | Signal |

| C1      | VCC                  | C5  | GND    |

| C2      | RST                  | C6  | VPP    |

| C3      | CLK                  | C7  | IO     |

## 2.2.6 M.2 E-Key (M2\_E1)

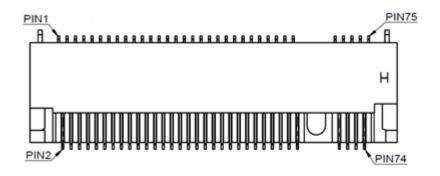

| Table | 2.6: M.2 E-Key (M2_E1) |     |                      |

|-------|------------------------|-----|----------------------|

| Pin   | Signal                 | Pin | Signal               |

| 1     | GND                    | 2   | +3.3V                |

| 3     | USB_D+                 | 4   | +3.3V                |

| 5     | USB_D-                 | 6   | WLAN_LED1#           |

| 7     | GND                    | 8   | BT_PCMCLK            |

| 9     | CNV_WR_D1-             | 10  | BT_PCMFRM            |

| 11    | CNV_WR_D1+             | 12  | BT_PCMIN             |

| 13    | GND                    | 14  | BT_PCMOUT            |

| 15    | CNV_WR_D0-             | 16  | BT_LED#              |

| 17    | CNV_WR_D0+             | 18  | GND                  |

| 19    | GND                    | 20  | UART WAKE#           |

| 21    | CNV_WR_CLK-            | 22  | CNV_BRI_RSP          |

| 23    | CNV_WR_CLK+            | 24  | Connector Key        |

| 25    | Connector Key          | 26  | Connector Key        |

| 27    | Connector Key          | 28  | Connector Key        |

| 29    | Connector Key          | 30  | Connector Key        |

| 31    | Connector Key          | 32  | CNV_RGI_DT_R         |

| 33    | GND                    | 34  | CNV_RGI_RSP          |

| 35    | PETp0                  | 36  | CNV_BRI_DT_R         |

| 37    | PETn0                  | 38  | CL_RST#              |

| 39    | GND                    | 40  | CL_DAT               |

| 41    | PERp0                  | 42  | CL_CLK               |

| 43    | PERn0                  | 44  | CNV_GNSS_PA_BLANKING |

| 45    | GND                    | 46  | CNV_MFUART2_TXD      |

| 47    | REFCLKp0               | 48  | CNV_MFUART2_RXD      |

| 49    | REFCLKn0               | 50  | SUSCLK               |

| 51    | GND                    | 52  | WLAN_RST#            |

| 53    | CLKREQ0#               | 54  | BT_RF_KILL#          |

| 55    | PEWAKE0#               | 56  | WIFI_RF_KILL#        |

| 57    | GND                    | 58  | NC                   |

| 59    | CNV_WT_D1-             | 60  | NC                   |

| 61    | CNV_WT_D1+             | 62  | NC                   |

| 63    | GND                    | 64  | NC                   |

| 65    | CNV_WT_D0-             | 66  | NC                   |

| 67    | CNV_WT_D0+             | 68  | NC                   |

|       |                        |     |                      |

| Table 2 | 2.6: M.2 E-Key (M2_E1) |    |       |

|---------|------------------------|----|-------|

| 69      | GND                    | 70 | NC    |

| 71      | CNV_WT_CLK-            | 72 | +3.3V |

| 73      | CNV_WT_CLK+            | 74 | +3.3V |

| 75      | GND                    |    |       |

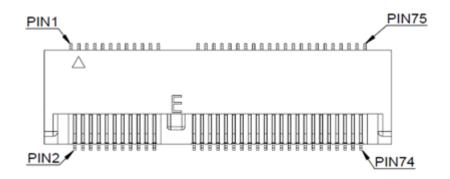

### 2.2.7 M.2 M-Key (M2\_M1)

| Table | 2.7: M.2 E-Key (M2_M1) |     |                                  |

|-------|------------------------|-----|----------------------------------|

| Pin   | Signal                 | Pin | Signal                           |

| 1     | GND                    | 2   | 3.3V                             |

| 3     | GND                    | 4   | 3.3V                             |

| 5     | PERn3                  | 6   | N/C                              |

| 7     | PERp3                  | 8   | N/C                              |

| 9     | GND                    | 10  | DAS/DSS# (I/O)/LED1# (I)(0/3.3V) |

| 11    | PETn3                  | 12  | 3.3V                             |

| 13    | PETp3                  | 14  | 3.3V                             |

| 15    | GND                    | 16  | 3.3V                             |

| 17    | PERn2                  | 18  | 3.3V                             |

| 19    | PERp2                  | 20  | N/C                              |

| 21    | GND                    | 22  | N/C                              |

| 23    | PETn2                  | 24  | N/C                              |

| 25    | PETp2                  | 26  | N/C                              |

| 27    | GND                    | 28  | N/C                              |

| 29    | PERn1                  | 30  | N/C                              |

| 31    | PERp1                  | 32  | N/C                              |

| 33    | GND                    | 34  | N/C                              |

| 35    | PETn1                  | 36  | N/C                              |

| 37    | PETp1                  | 38  | DEVSLP (O)                       |

| 39    | GND                    | 40  | N/C                              |

| 41    | PERn0/SATA-B+          | 42  | N/C                              |

| 43    | PERp0/SATA-B-          | 44  | N/C                              |

| 45    | GND                    | 46  | N/C                              |

| 47    | PETn0/SATA-A-          | 48  | N/C                              |

| 49    | PETp0/SATA-A+          | 50  | PERST# (O)(0/3.3V) or N/C        |

| 51    | GND                    | 52  | CLKREQ# (I/O)(0/3.3V) or N/C     |

| 53    | REFCLKn                | 54  | PEWAKE# (I/O)(0/3.3V) or N/C     |

| 55    | REFCLKp                | 56  | N/C                              |

| Table | e 2.7: M.2 E-Key (M2_M1) |    |                           |

|-------|--------------------------|----|---------------------------|

| 57    | GND                      | 58 | N/C                       |

| 59    | Connector Key            | 60 | Connector Key             |

| 61    | Connector Key            | 62 | Connector Key             |

| 63    | Connector Key            | 64 | Connector Key             |

| 65    | Connector Key            | 66 | Connector Key             |

| 67    | N/C                      | 68 | SUSCLK(32kHz) (O)(0/3.3V) |

| 69    | PEDET (NC-PCIe/GND-SATA) | 70 | 3.3V                      |

| 71    | GND                      | 72 | 3.3V                      |

| 73    | GND                      | 74 | 3.3V                      |

| 75    | GND                      |    |                           |

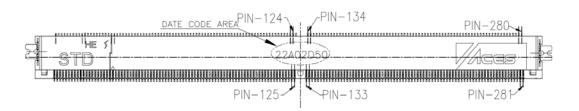

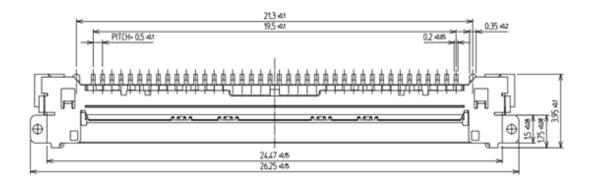

### 2.2.8 MXM (MXM16-1)

### 2.2.9 Audio (AUDIO1)

| Table 2.8: Audio (A | AUDIO1)  |

|---------------------|----------|

| Pin                 | Signal   |

| 1                   | MIC IN   |

| 2                   | LINE OUT |

### 2.2.10 DisplayPort (DP1)

| Table | 2.9: DisplayPort (DP1) |     |        |

|-------|------------------------|-----|--------|

| Pin   | Signal                 | Pin | Signal |

| 1     | DP1_0+                 | 2   | GND    |

| 3     | DP1_0-                 | 4   | DP1_1+ |

| 5     | GND                    | 6   | DP1_1- |

| 7     | DP1_2+                 | 8   | GND    |

| 9     | DP1_2-                 | 10  | DP1_3+ |

| 11    | GND                    | 12  | DP1_3- |

| 13    | DP1_HDMI_DNG_DET       | 14  | GND    |

| 15    | DP1_AUX+               | 16  | GND    |

| 17    | DP1_AUX-               | 18  | HPD    |

| 19    | GND                    | 20  | POWER  |

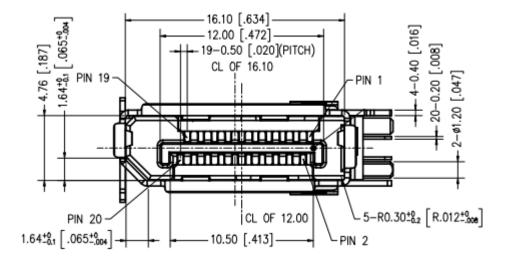

## 2.2.11 Dual DisplayPort (DP2\_DP3)

| Table 2 | 10: Dual DisplayPort (DP2_I | OP3) |                  |

|---------|-----------------------------|------|------------------|

| Pin     | Signal                      | Pin  | Signal           |

| P1      | DP3_0+                      | P21  | DP2_0+           |

| P2      | GND                         | P22  | GND              |

| P3      | DP3_0-                      | P23  | DP2_0-           |

| P4      | DP3_1+                      | P24  | DP2_1+           |

| P5      | GND                         | P25  | GND              |

| P6      | DP3_1-                      | P26  | DP2_1-           |

| P7      | DP3_2+                      | P27  | DP2_2+           |

| P8      | GND                         | P28  | GND              |

| P9      | DP3_2-                      | P29  | DP2_2-           |

| P10     | DP3_3+                      | P30  | DP2_3+           |

| P11     | GND                         | P31  | GND              |

| P12     | DP3_3-                      | P32  | DP2_3-           |

| P13     | DP3_HDMI_DNG_DET            | P33  | DP2_HDMI_DNG_DET |

| P14     | GND                         | P34  | GND              |

| P15     | DP3_AUX+                    | P35  | DP2_AUX+         |

| P16     | GND                         | P36  | GND              |

| P17     | DP3_AUX-                    | P37  | DP2_AUX-         |

| P18     | DP3_HPD                     | P38  | DP2_HPD          |

| P19     | GND                         | P39  | GND              |

| P20     | +3.3V_DP3                   | P40  | +3.3V_DP         |

### 2.2.12 USB Port 1234 (USB1234)

| Table 2.11: USB Port 1234 (USB1234) |                |     |                |

|-------------------------------------|----------------|-----|----------------|

| Pin                                 | Signal         | Pin | Signal         |

| 11                                  | +USBV1         | 12  | D1-            |

| 13                                  | D1+            | 14  | GND            |

| 15                                  | USB31_P1_z_RX- | 16  | USB31_P1_z_RX+ |

| 17                                  | GND            | 18  | USB31_P1_z_TX- |

| 19                                  | USB31_P1_z_TX+ |     |                |

| 21                                  | USBV2          | 22  | D2-            |

| 23                                  | D2+            | 24  | GND            |

| 25                                  | USB31_P2_z_RX- | 26  | USB31_P2_z_RX+ |

| 27                                  | GND            | 28  | USB31_P2_z_TX- |

| 29                                  | USB31_P2_z_TX+ |     |                |

| 31                                  | USBV3          | 32  | D3-            |

| 33                                  | D3+            | 34  | GND            |

| 35                                  | USB31_P3_z_RX- | 36  | USB31_P3_z_RX+ |

| 37                                  | GND            | 38  | USB31_P3_z_TX- |

| 39                                  | USB31_P3_z_TX+ | 40  |                |

| 41                                  | USBV4          | 42  | D4-            |

| 43                                  | D4+            | 44  | GND            |

| 45                                  | USB31_P4_z_RX- | 46  | USB31_P4_z_RX+ |

| 47                                  | GND            | 48  | USB31_P4_z_TX- |

| 49                                  | USB31_P4_z_TX+ |     |                |

### 2.3 Box Header

### 2.3.1 COM1 Connector (COM1)

| Table 2.12: COM1 Connector (COM1) |                  |     |                  |

|-----------------------------------|------------------|-----|------------------|

| Pin                               | Signal           | Pin | Signal           |

| 1                                 | COM1_422_485_TX- | 2   | COM1_422_485_TX+ |

| 3                                 | COM1_422_RX+     | 4   | COM1_422_RX-     |

| 5                                 | GND              | 6   | COM1_DSR#        |

| 7                                 | COM1_RTS#        | 8   | COM1_CTS#        |

| 9                                 | COM1_RI#         | 10  | NC               |

### 2.3.2 COM2 Connector (COM2)

| Table 2.13: COM2 Connector (COM2) |                  |     |                  |

|-----------------------------------|------------------|-----|------------------|

| Pin                               | Signal           | Pin | Signal           |

| 1                                 | COM2_422_485_TX- | 2   | COM2_422_485_TX+ |

| 3                                 | COM2_422_RX+     | 4   | COM2_422_RX-     |

| 5                                 | GND              | 6   | COM2_DSR#        |

| 7                                 | COM2_RTS#        | 8   | COM2_CTS#        |

| 9                                 | COM2_RI#         | 10  | NC               |

### 2.3.3 EDP/LVDS Connector (EDP1\_LVDS1)

| Table 2.14: LVDS P | Pin Definitions |

|--------------------|-----------------|

| Pin                | Signal          |

| 1                  | LVDS1_CTRL      |

| 2                  | GND             |

| 3                  | CH7511_CLK1N    |

| 4                  | CH7511_CLK1P    |

| 5                  | GND             |

| 6                  | CH7511_A0N_C    |

| 7                  | CH7511_A0P_C    |

| 8                  | GND             |

| 9                  | CH7511_A1N_C    |

| 10                 | CH7511_A1P_C    |

| 11                 | GND             |

| 12                 | CH7511_A2N_C    |

| 13                 | CH7511_A2P_C    |

| 14                 | GND             |

| 15                 | NC              |

| 16                 | NC              |

| 17                 | GND             |

| 18                 | LVDS1_A3N_C     |

| 19                 | LVDS1_A3P_C     |

| 20                 | GND             |

| 21                 | LVDS1_CLK2N     |

| 22                 | LVDS1_CLK2P     |

| 23                 | GND             |

| 24                 | LVDS1_A7N_C     |

| 25                 | LVDS1_A7P_C     |

| 26                 | GND             |

| 27                 | LVDS1_A6N_C     |

| 28                 | LVDS1_A6P_C     |

| 29                 | GND             |

| 30                 | LVDS1_A5N_C     |

| 31                 | LVDS1_A5P_C     |

| 32                 | GND             |

| 33                 | LVDS1_A4N_C     |

| Table 2.14: LVDS Pin Definitions |             |  |

|----------------------------------|-------------|--|

| 34                               | LVDS1_A4P_C |  |

| 35                               | NC          |  |

| 36                               | GND         |  |

| 37                               | VDD_LVDS1   |  |

| 38                               | VDD_LVDS1   |  |

| 39                               | VDD_LVDS1   |  |

| 40                               | VDD_LVDS1   |  |

| Table 2.15: eDP Pi | n Definitions |

|--------------------|---------------|

| Pin                | Signal        |

| 1                  | LVDS1_CTRL    |

| 2                  | GND           |

| 3                  | AUX_CH_N      |

| 4                  | AUX_CH_P      |

| 5                  | GND           |

| 6                  | NC            |

| 7                  | HPD           |

| 8                  | GND           |

| 9                  | Lane1_N       |

| 10                 | Lane1_P       |

| 11                 | GND           |

| 12                 | Lane0_N       |

| 13                 | Lane0_P       |

| 14                 | GND           |

| 17                 | GND           |

| 20                 | GND           |

| 23                 | GND           |

| 26                 | GND           |

| 29                 | GND           |

| 32                 | GND           |

| 35                 | NC            |

| 36                 | NC            |

| 37                 | VDD_LVDS1     |

| 38                 | VDD_LVDS1     |

| 39                 | VDD_LVDS1     |

| 40                 | VDD_LVDS1     |

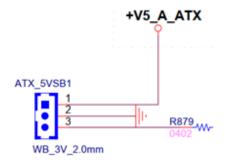

### 2.3.4 ATX 5V/PSON Connector (ATX\_5VSB1)

| Table 2.16: ATX 5V/PSON Connector (ATX_5VSB1) |            |  |

|-----------------------------------------------|------------|--|

| Pin                                           | Signal     |  |

| 1                                             | +5V_A_ATX  |  |

| 2                                             | GND        |  |

| 3                                             | SPS_PS_ON# |  |

### 2.3.5 EDP/LVDS Backlight Inverter Power Connector (INV1)

| Table 2.17: EDP/LVDS Backlight Inverter Power Connector (INV1) |          |  |

|----------------------------------------------------------------|----------|--|

| Pin                                                            | Signal   |  |

| 1                                                              | +12V     |  |

| 2                                                              | GND      |  |

| 3                                                              | BKL EN   |  |

| 4                                                              | BKL CTRL |  |

| 5                                                              | +5V      |  |

### 2.3.6 USB 56 (USB56)

| <b>Table</b> | 2.18: USB 56 (USB56) |     |        |

|--------------|----------------------|-----|--------|

| Pin          | Signal               | Pin | Signal |

| 1            | N.C                  | 2   | GND    |

| 3            | GND                  | 4   | GND    |

| 5            | D+                   | 6   | D+     |

| 7            | D-                   | 8   | D-     |

| 9            | VBUS                 | 10  | VBUS   |

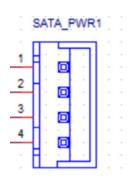

### 2.3.7 SATA Power (SATA\_PWR1)

| Table 2.19: SATA Power (SATA_PWR1) |        |  |

|------------------------------------|--------|--|

| Pin                                | Signal |  |

| 1                                  | +V5    |  |

| 2                                  | GND    |  |

| 3                                  | GND    |  |

| 4                                  | +V12   |  |

## 2.4 Pin Header

# 2.4.1 Power LED Pin Header (JFP2)

| Table 2.20: Power LED Pin Header (JFP2) |            |  |

|-----------------------------------------|------------|--|

| Pin                                     | Signal     |  |

| 1                                       | Power LED+ |  |

| 2                                       | NC         |  |

| 3                                       | Power LED- |  |

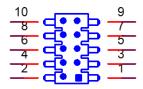

# 2.4.2 General Purpose I/O Pin Header (GPIO1)

| Table 2.21: General Purpose I/O Pin Header (GPIO1) |          |     |        |

|----------------------------------------------------|----------|-----|--------|

| Pin                                                | Signal   | Pin | Signal |

| 1                                                  | GPIO0    | 2   | GPIO4  |

| 3                                                  | GPIO1    | 4   | GPIO5  |

| 5                                                  | GPIO2    | 6   | GPIO6  |

| 7                                                  | GPIO3    | 8   | GPI07  |

| 9                                                  | VCC_GPIO | 10  | GND    |

## 2.4.3 CPUFAN (CPUFAN1)

| Table 2.22: CPUFAN (CPUFAN1) |               |  |

|------------------------------|---------------|--|

| Pin                          | Signal        |  |

| 1                            | GND           |  |

| 2                            | CPU FAN VCC   |  |

| 3                            | CPU FAN SPEED |  |

| 4                            | CPU FAN PWM   |  |

## 2.4.4 SYSFAN (SYSFAN1)

| Table 2.23: SYSFAN (SYSFAN1) |                  |  |

|------------------------------|------------------|--|

| Pin                          | Signal           |  |

| 1                            | GND              |  |

| 2                            | SYSTEM FAN VCC   |  |

| 3                            | SYSTEM FAN SPEED |  |

| 4                            | SYSTEM FAN PWM   |  |

## 2.4.5 SYSFAN (SYSFAN2)

| Table 2.24: SYSFAN (SYSFAN2) |                  |  |

|------------------------------|------------------|--|

| Pin                          | Signal           |  |

| 1                            | GND              |  |

| 2                            | SYSTEM FAN VCC   |  |

| 3                            | SYSTEM FAN SPEED |  |

| 4                            | SYSTEM FAN PWM   |  |

## 2.4.6 AMP (AMP 1)

| Table 2.25: AMP (AMP 1) |              |  |

|-------------------------|--------------|--|

| Pin                     | Signal       |  |

| 1                       | AMP OUT – R+ |  |

| 2                       | AMP OUT – R- |  |

| 3                       | AMP OUT – L- |  |

| 4                       | AMP OUT – L+ |  |

# 2.4.7 Program VCORE Header (VR\_PMB1)

| Table 2.26: Program VCORE Header (VR_PMB1) |        |  |

|--------------------------------------------|--------|--|

| Pin                                        | Signal |  |

| 1                                          | DATA   |  |

| 2                                          | GND    |  |

| 3                                          | CLK    |  |

## **2.4.8 MXM FAN (MXMFAN1)**

| Table 2.27: MXM FAN (MXMFAN1) |               |  |

|-------------------------------|---------------|--|

| Pin                           | Signal        |  |

| 1                             | GND           |  |

| 2                             | MXM FAN VCC   |  |

| 3                             | MXM FAN SPEED |  |

| 4                             | MXM FAN PWM   |  |

# 2.5 Jumper Settings

## 2.5.1 Front Panel Header (JFP1)

| Table 2.28: Front Panel Header (JFP1) |                |     |               |

|---------------------------------------|----------------|-----|---------------|

| Pin                                   | Signal         | Pin | Signal        |

| 1                                     | 3.3V           | 2   | FP_PANSWIN#   |

| 3                                     | FP_HDD_LED#    | 4   | GND           |

| 5                                     | SMB_DAT_RESUME | 6   | FP_SYS_RESET# |

| 7                                     | SMB_CLK_RESUME | 8   | GND           |

## 2.5.2 CMOS Reset Header (JCMOS1)

| Table 2.29: CMOS Reset Header (JCMOS1) |            |  |

|----------------------------------------|------------|--|

| Pin                                    | Signal     |  |

| 1                                      | NC         |  |

| 2                                      | RTCRST#    |  |

| 3                                      | RTCRST#_PD |  |

# 2.5.3 AT/ATX Mode Selection (PSON1)

| Table 2.30: AT/ATX Mode Selection (PSON1) |               |  |

|-------------------------------------------|---------------|--|

| Pin                                       | Signal        |  |

| 1                                         | VCCAT         |  |

| 2                                         | +V3_Pull High |  |

| 3                                         | VCCATX        |  |

## 2.5.4 EDP Panel / LVDS Panel Voltage Selection (JEDP1\_LVDS1)

| Table 2.31: EDP Panel / LVDS Panel Voltage Selection (JEDP1_LVDS1) |        |     |        |

|--------------------------------------------------------------------|--------|-----|--------|

| Pin                                                                | Signal | Pin | Signal |

| 1                                                                  | NC     | 2   | +5V    |

| 3                                                                  | +12V   | 4   | VDD    |

| 5                                                                  | NC     | 6   | +3.3V  |

## 2.5.5 Program EC Header (JEC1)

Chapter

**BIOS Operation**

### 3.1 Introduction

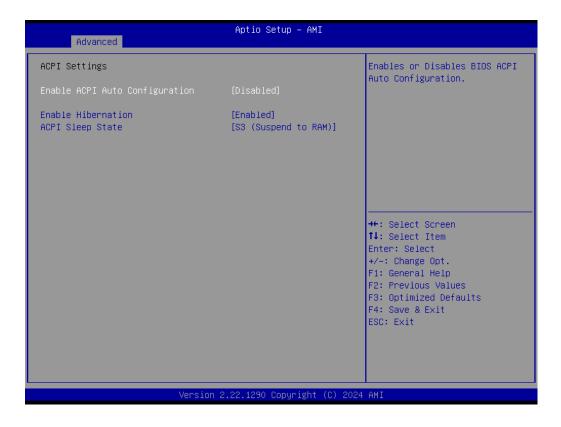

With the AMI BIOS Setup program, you can modify BIOS settings and control the special features of your computer. The Setup program uses a number of menus for making changes and turning special features on or off. This chapter describes the basic navigation of the AIMB-292 setup screens.

## 3.2 BIOS Setup

The AIMB-292 Series system has AMI BIOS built in, with a CMOS SETUP utility that allows users to configure required settings or to activate certain system features. The CMOS SETUP saves the configuration in the CMOS RAM of the motherboard. When the power is turned off, the battery on the board supplies the necessary power to preserve the CMOS RAM.

When the power is turned on, press the <Del> button during the BIOS POST (Power-On Self-Test) to access the CMOS SETUP screen.

| Table 3.1: Control Keys    |                                                                                                         |  |

|----------------------------|---------------------------------------------------------------------------------------------------------|--|

| < ↑ >< ↓ >< ← >< → >       | Move to select item                                                                                     |  |

| <enter></enter>            | Select Item                                                                                             |  |

| <esc></esc>                | Main Menu - Quit and not save changes into CMOS<br>Sub-menu - Exit current page and return to Main Menu |  |

| <page +="" up=""></page>   | Increase the numeric value or make changes                                                              |  |

| <page .="" down=""></page> | Decrease the numeric value or make changes                                                              |  |

| <f1></f1>                  | General help, for Setup Sub-menu                                                                        |  |

| <f2></f2>                  | Item Help                                                                                               |  |

| <f5></f5>                  | Load Previous Values                                                                                    |  |

| <f7></f7>                  | Load Setup Defaults                                                                                     |  |

| <f10></f10>                | Save all CMOS changes                                                                                   |  |

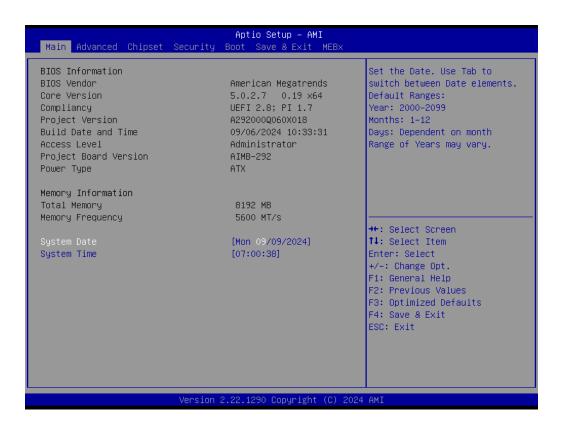

### 3.2.1 Main Menu

Press <Del> to enter the AMI BIOS CMOS Setup Utility. The Main Menu will appear on the screen. Use the arrow keys to select among the items and press <Enter> to accept or enter the sub-menu.

The Main BIOS setup screen has two main frames. The left frame displays all the options that can be configured. Grayed-out options cannot be configured; options in blue can. The right frame displays the legend. Above the legend is an area reserved for a text message. When an option is selected in the left frame, it is highlighted in white. Often a text message will accompany it.

### System Time / System Date

Use this option to change the system time and date. Highlight the System Time or System Date using the <Arrow> keys. Enter new values via the keyboard. Press the <Tab> or <Arrow> keys to move between fields. The date must be entered in MM/DD/YY format. The time must be entered in HH:MM:SS format.

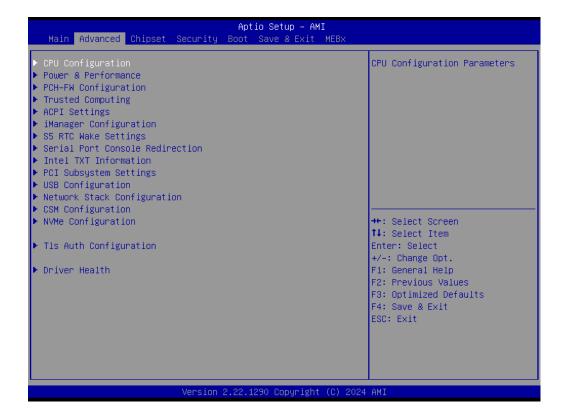

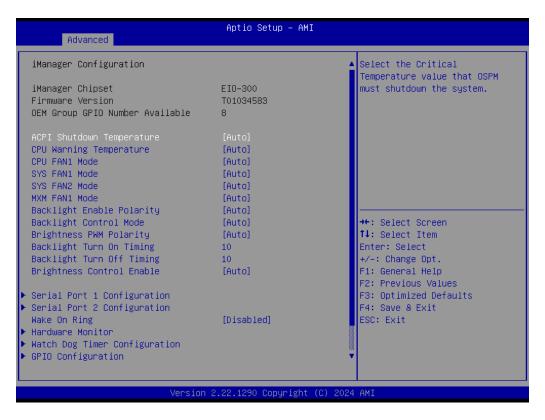

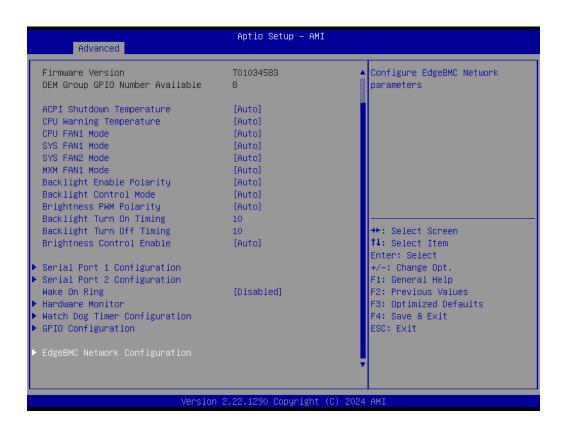

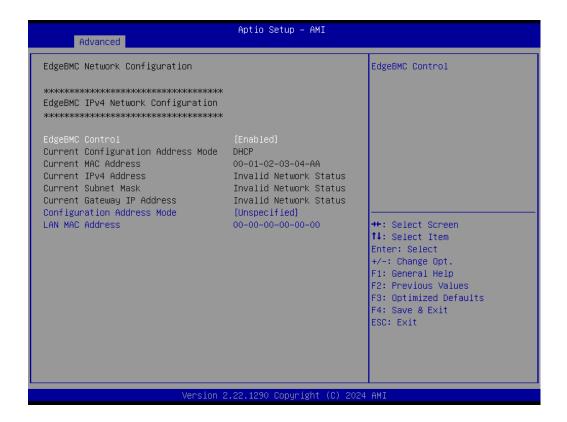

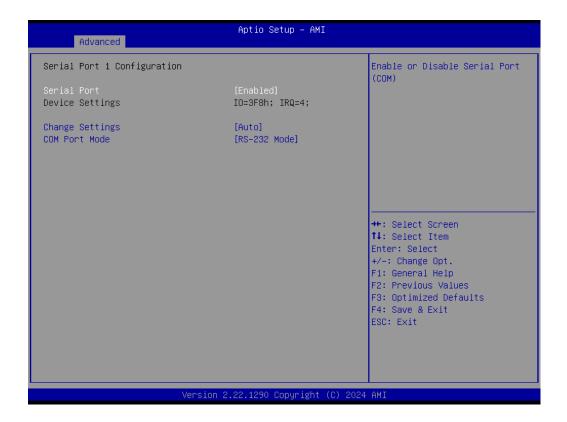

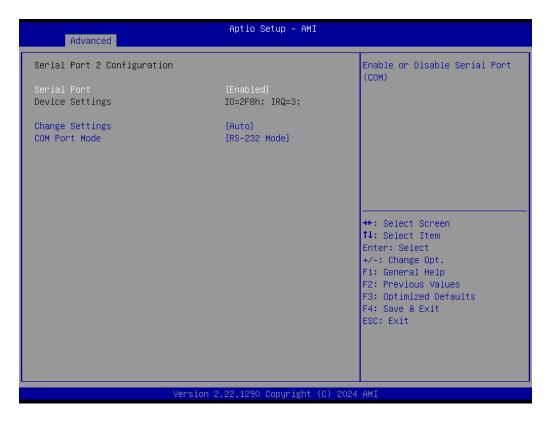

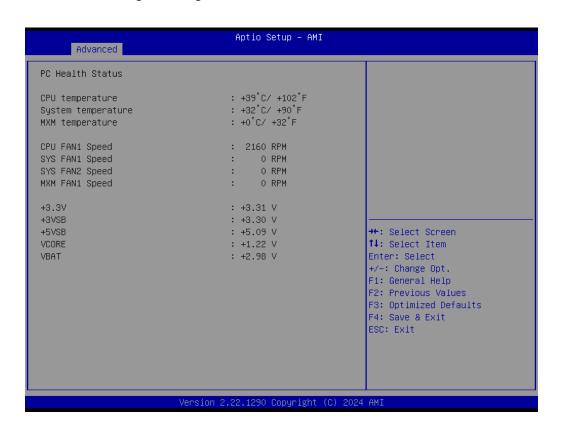

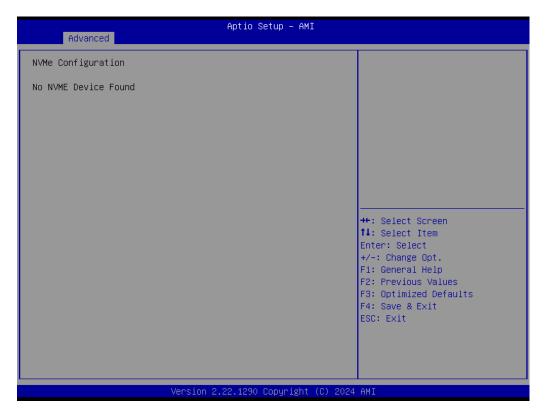

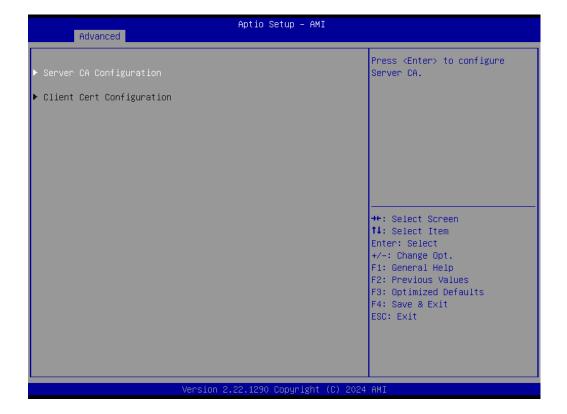

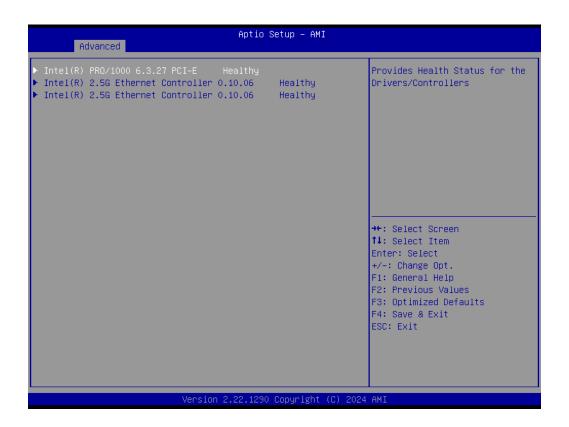

### 3.2.2 Advanced BIOS Features

Select the Advanced tab from the AIMB-292 setup menu to enter the Advanced BIOS setup page. Users can select any item in the left frame of the screen, such as CPU configuration. Select an Advanced BIOS setup option by highlighting the text using the <Arrow> keys. All Advanced BIOS setup options are described in this section. The Advanced BIOS setup menu screen is shown below. The sub-menus are described in the following pages.

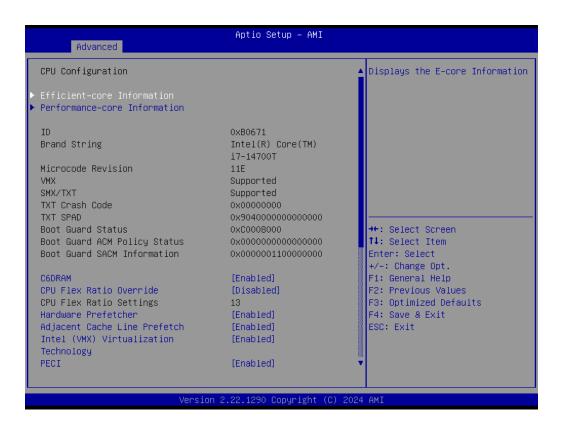

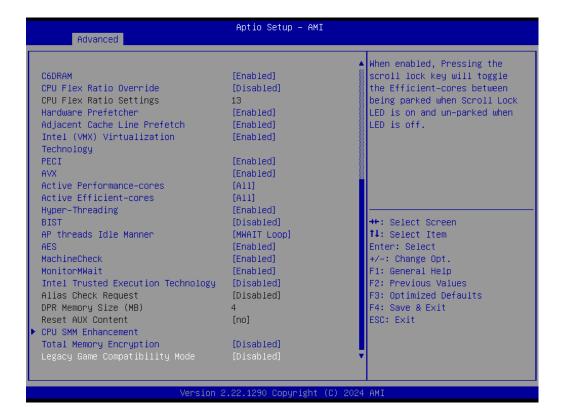

### 3.2.2.1 CPU Configuration

Advanced → CPU Configuration

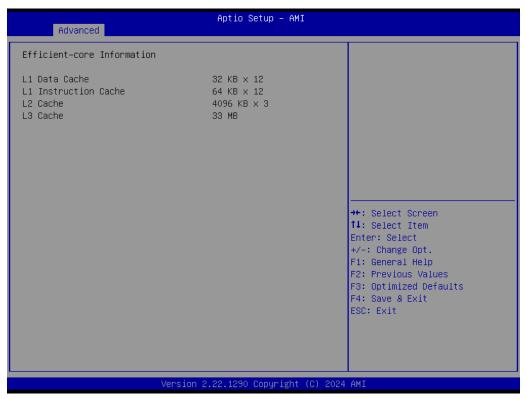

### **Efficient-core Information**

Advanced → CPU Configuration → Efficient-core Information

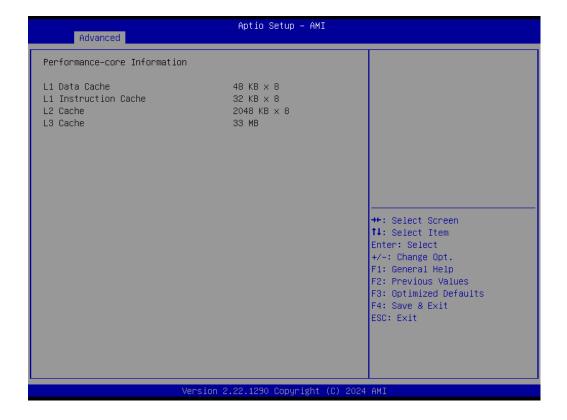

### **Performance-core Information**

Advanced → CPU Configuration → Performance-core Information

### **CPU SMM Enhancement**

Advanced → CPU SMM Enhancement

- SMM Use Delay Indication [Enable]

Enable/Disable usage of SMM DELAYED MSR for MP sync in SMI.

- SMM Use Block Indication [Enable]

- SMM Use SMM en-US Indication [Enable]

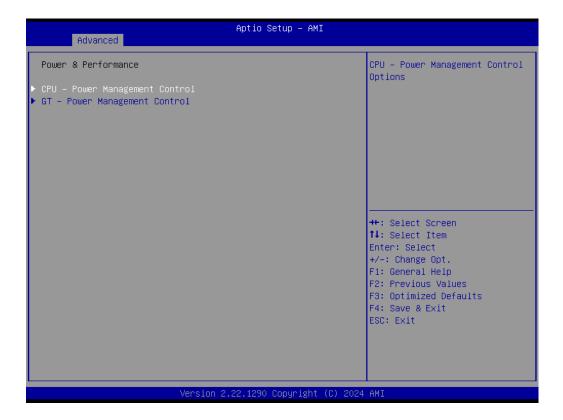

### 3.2.2.2 Power & Performance

Advanced → Power & Performance

- CPU Power Management Control CPU Power Management Control Options.

- GT Power Management Control

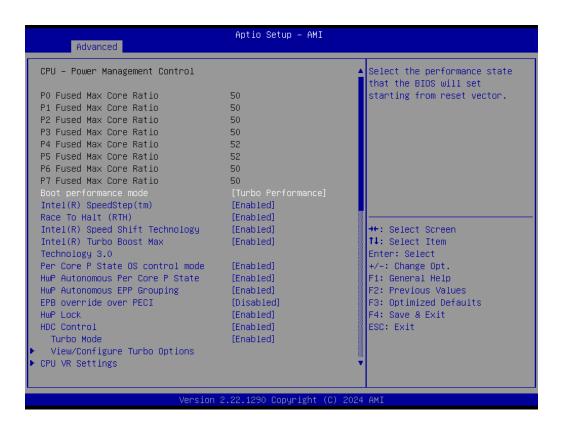

### **CPU – Power Management Control**

Advanced → Power & Performance → CPU – Power Management Control

### ■ Boot performance mode [Turbo Performance]

Select the performance state that the BIOS will set starting from the reset vector.

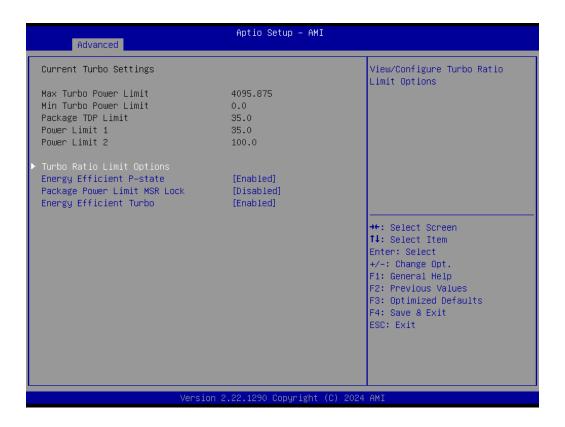

### **Current Turbo Settings**

Advanced  $\rightarrow$  Power & Performance  $\rightarrow$  CPU – Power Management Control  $\rightarrow$  View/ Configure Turbo Ratio

### **Turbo Ratio Limit Options**

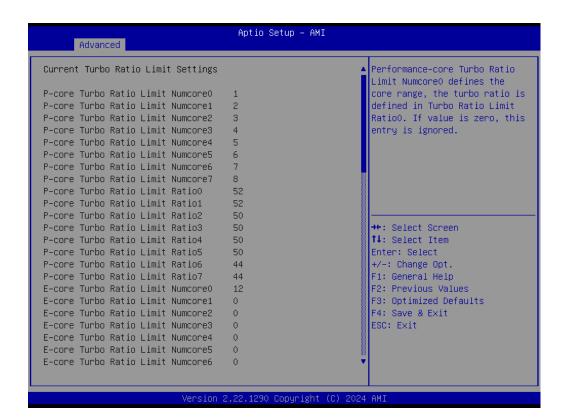

Advanced → Power & Performance → CPU – Power Management Control → View/ Configure Turbo Ratio → Turbo Ratio Limit Options

### **Turbo Ratio Limit Options** View/Configure Turbo Ratio Limit Options.

- Energy Efficient P-state [Enable]

- Package Power Limit MSR Lock [Disabled]

- Power Limit 1 Override [Disabled]

- Power Limit 2 Override [Enabled]

- Power Limit 2 0

- Energy Efficient P-state [Disable]

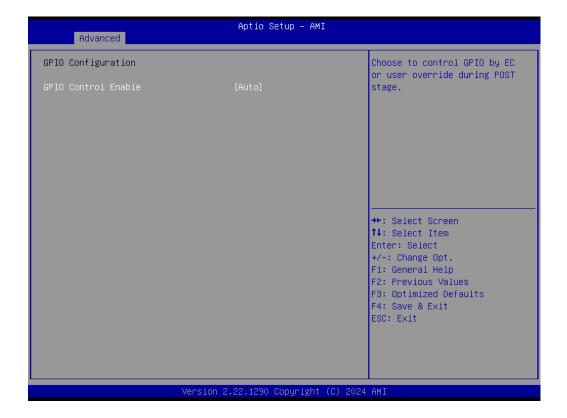

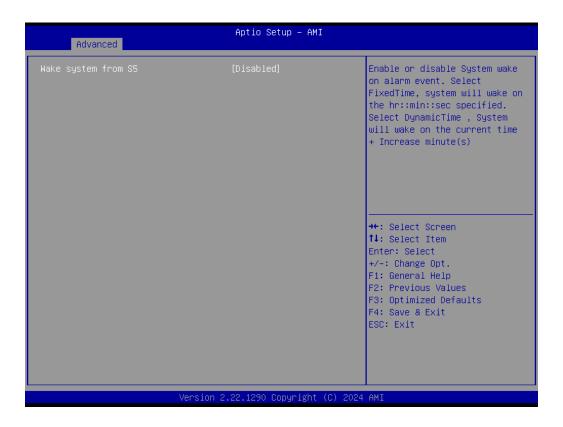

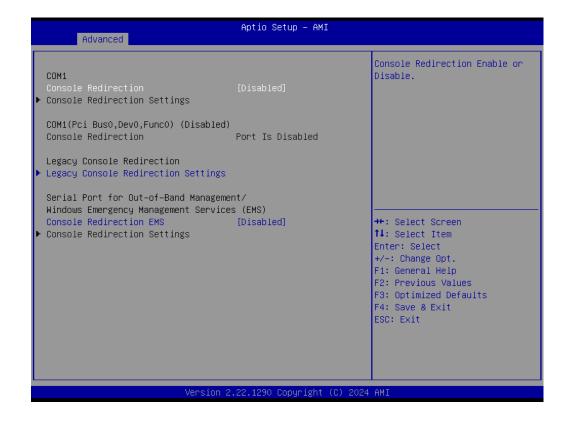

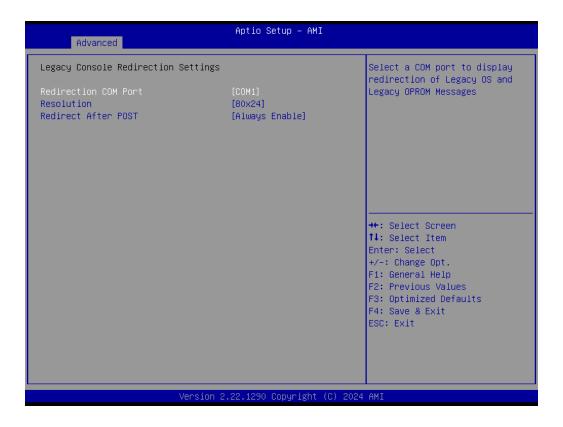

Aptio Setup – AMI Advanced E-core Turbo Ratio Limit Numcore7 Performance–core Turbo Ratio E-core Turbo Ratio Limit Ratio0 Limit Ratio6 defines the turbo 37 E-core Turbo Ratio Limit Ratio1 0 ratio (max is 85 in normal E-core Turbo Ratio Limit Ratio2 0 mode and 120 in core extension E-core Turbo Ratio Limit Ratio3 mode), the core range is E-core Turbo Ratio Limit Ratio4 defined in Turbo Ratio Limit 0 E-core Turbo Ratio Limit Ratio5 Numcore6 Λ E-core Turbo Ratio Limit Ratio6 E-core Turbo Ratio Limit Ratio7 P-core Turbo Ratio Limit NumcoreO P-core Turbo Ratio Limit Numcore1 P-core Turbo Ratio Limit Numcore2 P-core Turbo Ratio Limit Numcore3 →+: Select Screen P-core Turbo Ratio Limit Numcore4 ↑↓: Select Item P-core Turbo Ratio Limit Numcore5 Enter: Select P-core Turbo Ratio Limit Numcore6 +/-: Change Opt. F1: General Help P-core Turbo Ratio Limit Numcore7 P-core Turbo Ratio Limit RatioO 52 F2: Previous Values P-core Turbo Ratio Limit Ratio1 F3: Optimized Defaults P-core Turbo Ratio Limit Ratio2 F4: Save & Exit P-core Turbo Ratio Limit Ratio3 50 ESC: Exit P-core Turbo Ratio Limit Ratio4 50 P-core Turbo Ratio Limit Ratio5

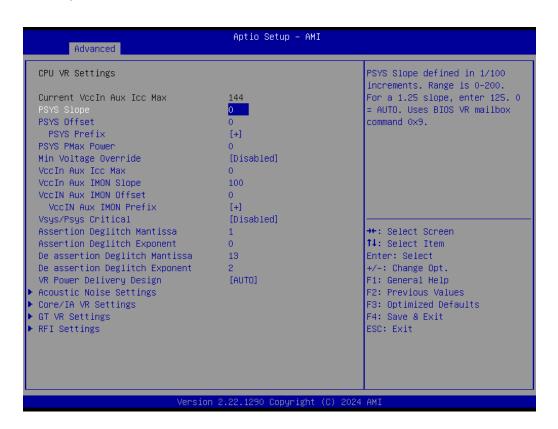

### **CPU VR Settings**

Advanced  $\rightarrow$  Power & Performance  $\rightarrow$  CPU – Power Management Control  $\rightarrow$  CPU VR Settings

### PSYS Slope

PSYS Slope is defined in 1/100 increments. The range is 0-200. For a 1.25 slope, enter 125. 0=Auto. Users BIOS VR mailbox command 0x9.

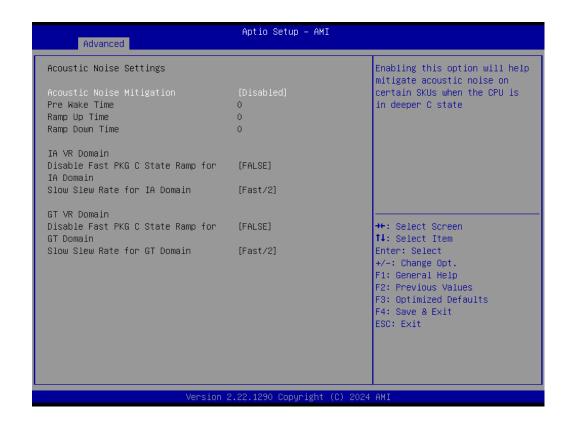

### **Acoustic Noise Settings**

Advanced → Power & Performance → CPU – Power Management Control → CPU VR Settings → Acoustic Noise Settings

### ■ Acoustic Noise Mitigation [Disabled]

Enabling this option will help mitigate acoustic noise on certain SKUs when the CPU is in a deeper C state.

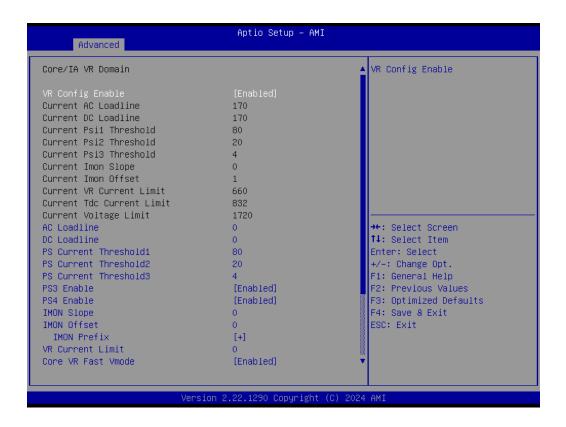

### Core/IA VR Settings

Advanced  $\rightarrow$  Power & Performance  $\rightarrow$  CPU – Power Management Control  $\rightarrow$  CPU VR Settings  $\rightarrow$  Core/IA Settings

# VR Config Enable [Enabled] VR Config Enable.

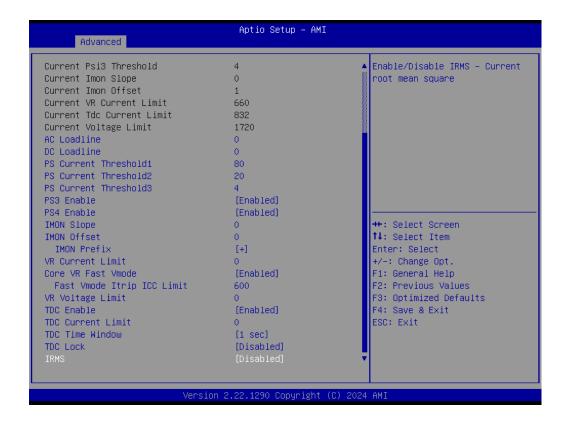

### IRMS [Disabled]

Enable/Disable IRMS - Current root mean square.

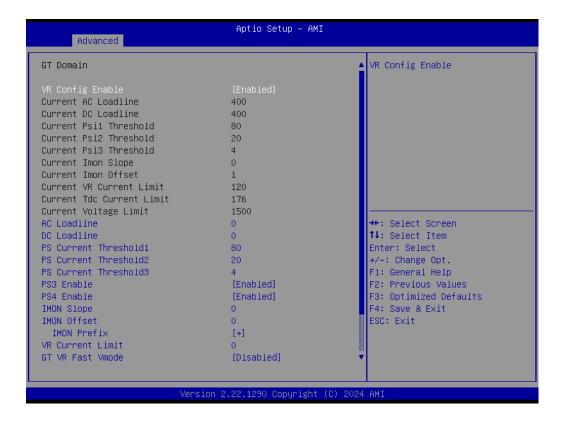

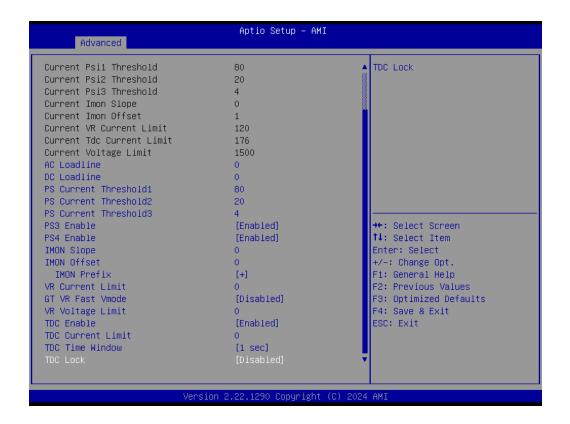

### **GT Domain**

Advanced  $\to$  Power & Performance  $\to$  CPU – Power Management Control  $\to$  CPU VR Settings  $\to$  GT Domain

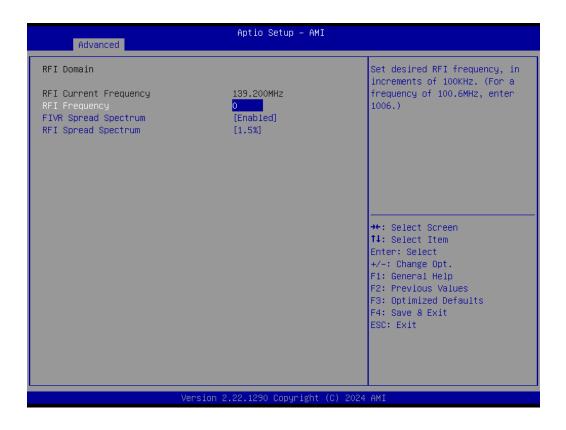

### **RFI Domain**

Advanced  $\rightarrow$  Power & Performance  $\rightarrow$  CPU – Power Management Control  $\rightarrow$  CPU VR Settings  $\rightarrow$  RFI Domain

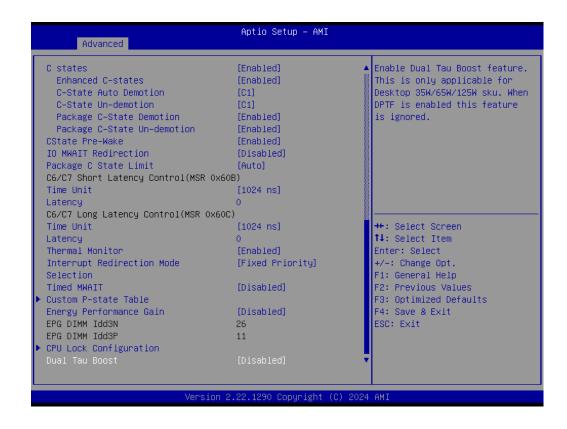

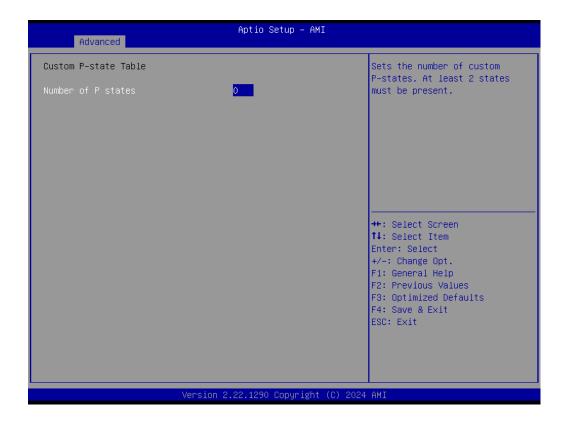

### **Custom P-state Table**

Advanced  $\rightarrow$  Power & Performance  $\rightarrow$  CPU – Power Management Control  $\rightarrow$  Custom P-state Table

### Number of P states 0

Sets the number of custom P-states. At least 2 states must be present.

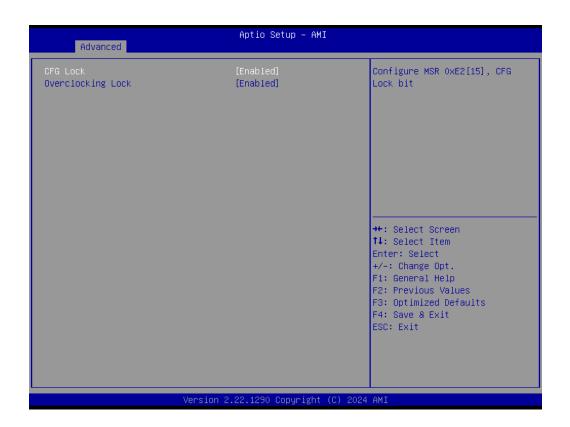

### **CFG Lock**

$\mathsf{Advanced} \to \mathsf{Power} \ \& \ \mathsf{Performance} \to \mathsf{CPU} - \mathsf{Power} \ \mathsf{Management} \ \mathsf{Control} \to \mathsf{CFG} \ \mathsf{Lock}$

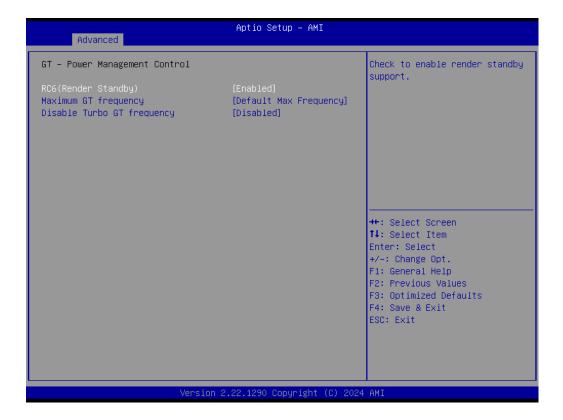

### **GT – Power Management Control**

Advanced → Power & Performance → GT – Power Management Control

- RC6 (Render Standby) [Enabled]

Check to enable render standby support.

- Maximum GT frequency [Default Max Frequency]

- Disable Turbo GT frequency [Disabled]

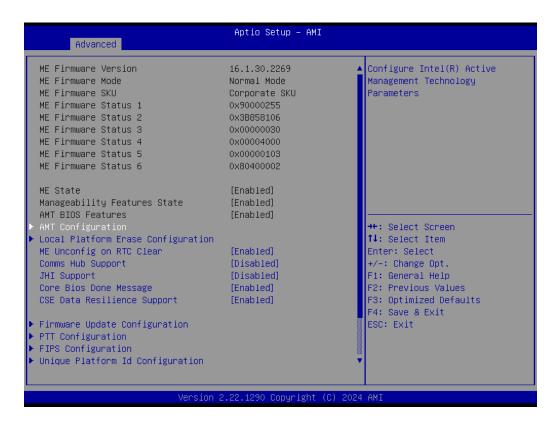

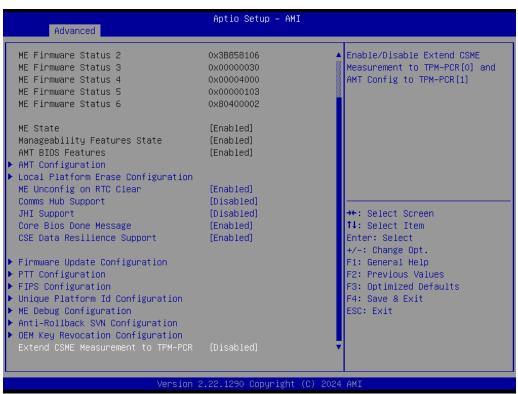

### 3.2.2.3 PCH-FW Configuration

### Advanced → PCH-FW Configuration

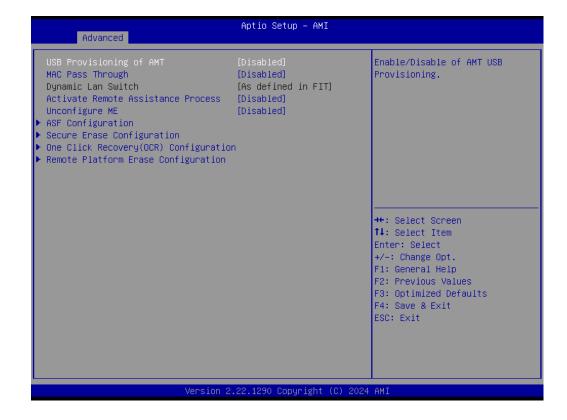

### **AMT Configuration**

Advanced → PCH-FW Configuration → AMT Configuration

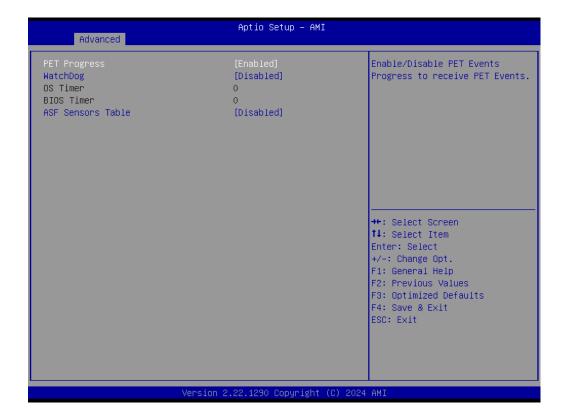

### **AMT Configuration**

Advanced→ PCH-FW Configuration → AMT Configuration → ASF Configuration

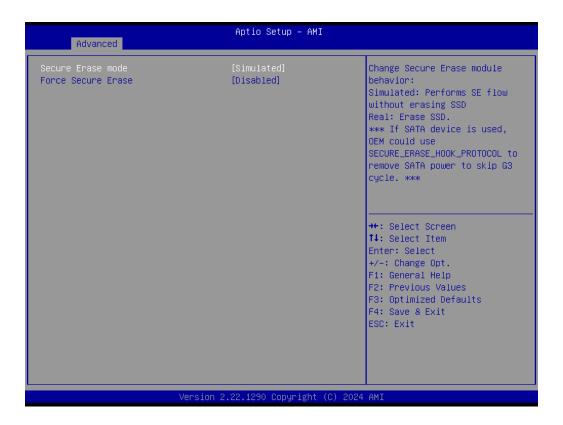

### **Secure Erase Configuration**

Advanced  $\rightarrow$  PCH-FW Configuration  $\rightarrow$  AMT Configuration  $\rightarrow$  Secure Erase Configuration

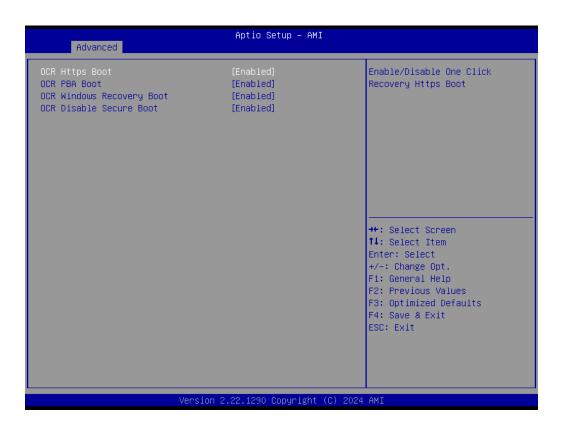

### One Click Recovery (OCR) Configuration

Advanced  $\to$  PCH-FW Configuration  $\to$  AMT Configuration  $\to$  One Click Recovery (OCR) Configuration

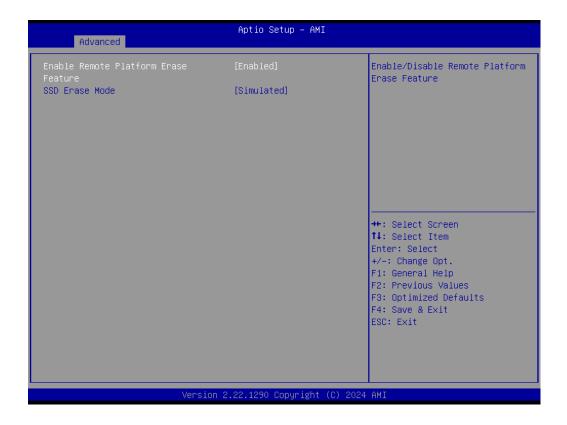

### **Enable Remote Platform Erase Feature**

Advanced  $\to$  PCH-FW Configuration  $\to$  AMT Configuration  $\to$  Enable Remote Platform Erase Feature

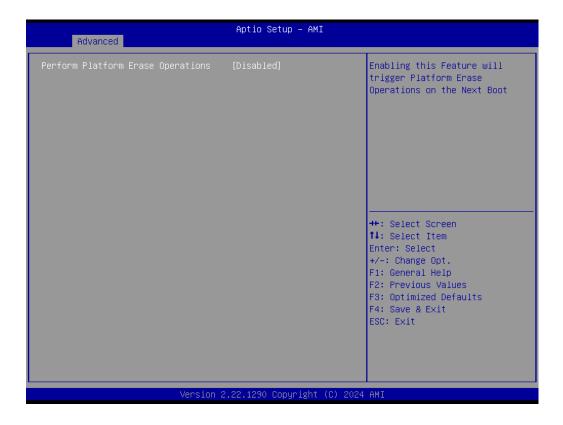

### **Performance Platform Erase Operations**

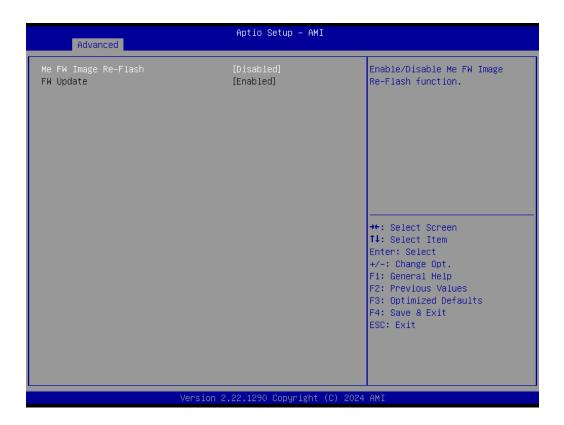

### **Firmware Update Configuration**

Advanced → PCH-FW Configuration → Firmware Update Configuration

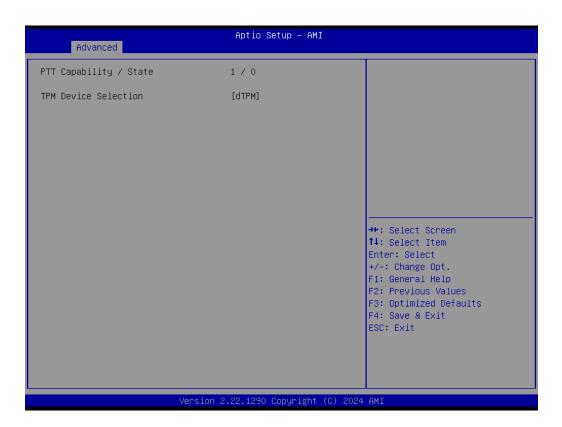

### **PTT Configuration**

Advanced → PCH-FW Configuration → PTT Configuration

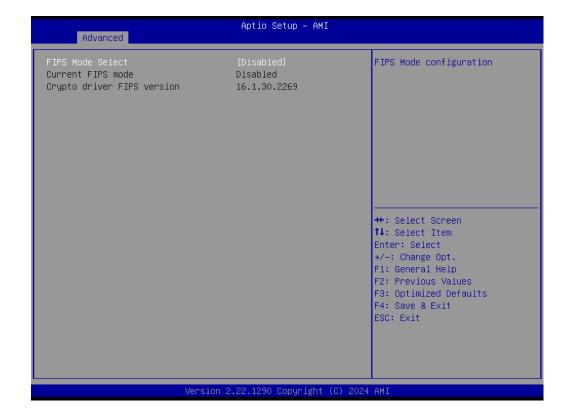

### **FIPS Configuration**

$Advanced \rightarrow PCH\text{-}FW\ Configuration \rightarrow FIPS\ Configuration$

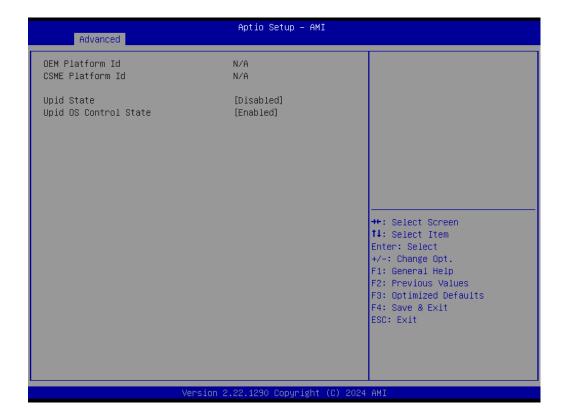

### **Unique Platform Id Configuration**

Advanced → PCH-FW Configuration → Unique Platform Id Configuration

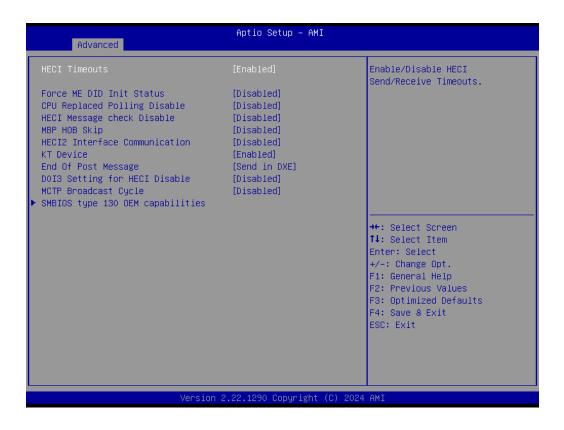

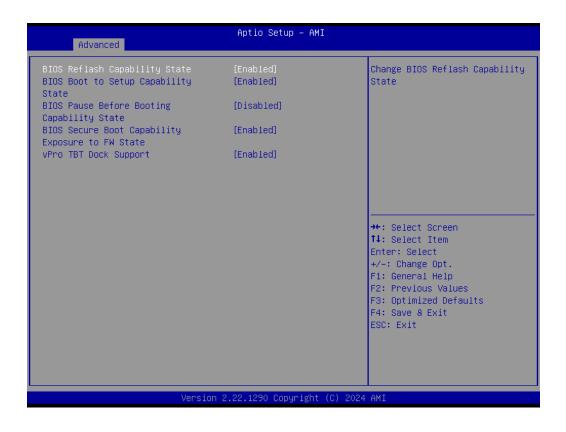

### **ME Debug Configuration**

Advanced → PCH-FW Configuration → ME Debug Configuration

### **SMBIOS Type 130 OEM Capabilities**

Advanced → PCH-FW Configuration → ME Debug Configuration → SMBIOS Type 130 OEM Capabilities

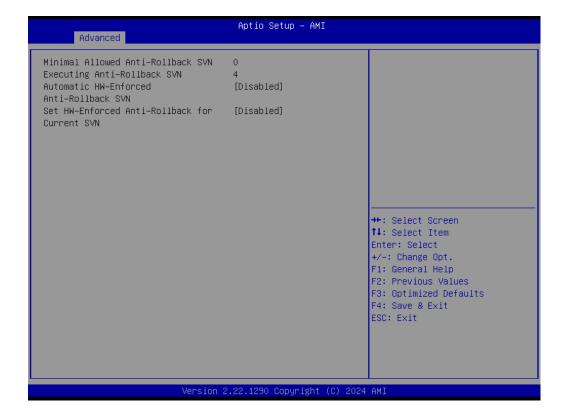

### **Anti-Rollback SVN Configuration**

Advanced → PCH-FW Configuration → Anti-Rollback SVN Configuration

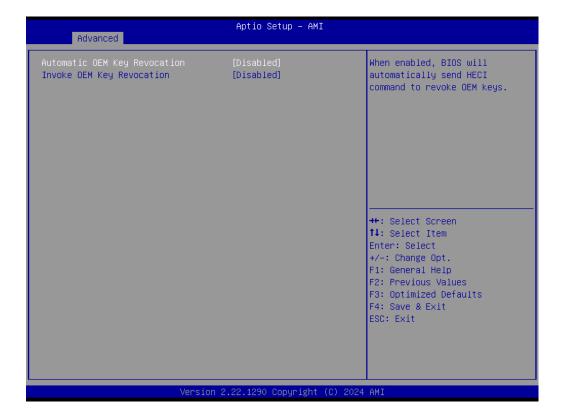

### **OEM Key Revocation Configuration**

Advanced → PCH-FW Configuration → OEM Key Revocation Configuration

## 3.2.2.4 Trusted Computing Settings

$Advanced \rightarrow Trusted \ Computing \\$

| Advanced                                                                                                                                                                                                                                                                                      | Aptio Setup – AMI                                                               |                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPM 2.0 Device Found Firmware Version: Vendor:  Security Device Support Active PCR banks Available PCR banks  SHA256 PCR Bank SHA384 PCR Bank Pending operation Platform Hierarchy Storage Hierarchy Endorsement Hierarchy Physical Presence Spec Version TPM 2.0 InterfaceType Device Select | 15.23 IFX  [Enable] SHA256 SHA256,SHA384  [Enabled] [Disabled] [None] [Enabled] | Enables or Disables BIOS support for security device. O.S. will not show Security Device. TCG EFI protocol and INT1A interface will not be available.   |