# 規格書 SPECIFICATION

品名

SWITCHING POWER SUPPLY

STYLE NAME:

型號

BP1H-5420V

MODEL NO.:

料號

PART NO.:

版次

A1

REVISION:

| APPROVE<br>核准    | # 3 W MAY 06, 2010 | 正式 |                           |

|------------------|--------------------|----|---------------------------|

| CHECK BY<br>審核   | 横松平州, 63010        | 資料 | (上京百行)<br>(MAY 0 6, 2010) |

| FORM MAKER<br>經辦 | 陳启文uar.6.son       | 用章 | 灰形太部                      |

新巨企業股份有限公司 電源事業處 ZIPPY TECHNOLOGY CORP. POWER DIVISION

10F,NO.50 MIN CHYUAN RD., SHIN TIEN CITY,TAIPEI HSIEN, TAIWAN,R.O.C.

TEL.: +886(2)29188512 FAX.: +886(2)29134969

## Revision

| Rev. | Page | Item | Date | Description |

|------|------|------|------|-------------|

|      |      |      |      |             |

### MODEL NO. BP1H-5420V

- 1.0 Scope

- 2.0 Input requirements

- 2.1 Voltage

- 2.2 Steady-state current

- 2.3 Inrush current

- 3.0 Output requirements

- 3.1 DC load requirements

- 3.2 Regulation

- 3.3 Ripple and noise

- 3.3.1 Specification

- 3.3.2 Ripple voltage test circuit

- 3.4 Overshoot

- 3.5 Efficiency

- 4.0 Protection

- 4.1 Input

- 4.2 Output

- 4.2.1 OPP

- 4.2.2 OVP

- 4.2.3 Short current

- 4.2.4 OCP

- 5.0 Power supply sequencing

- 5.1 Turn on

- 5.2 Hold up time

- 5.3 Power off sequence

- 6.0 Signal requirements

- 6.1 Power good signal

- 7.0 Environment

- 7.1 Temperature

- 7.2 Humidity

- 7.3 Insulation resistance

- 7.4 Dielectric withstanding voltage

- 8.0 Safety

- 8.1 UL

- 8.2 TUV

- 8.3 CB

- 9.0 Reliability

- 9.1 Burn in

- 10.0 Mechanical requirements

- 11.0 DC output cable drawing

#### 1.0 Scope

This specification defines the performance characteristics of a grounded 420 watts • 5 output level power supply. This specification also defines world wide safety requirements and manufactures process test requirements.

#### 2.0 Input requirements

2.1 Voltage

Range

$18 \sim 36 \text{ VDC}$

Nomal

24VDC

#### 2.2 Steady-state current

$18 \sim 36 \, \text{VDC} / 33 \sim 16 \, \text{amp} \, (24 \, \text{amp at} \, 24 \, \text{VDC})$

2.3 Inrush current

50 amps @ 24VDC (at 25 degrees ambient cold start)

#### 3.0 Output requirements

#### 3.1 DC load requirements

| Normal         | Load | current | Regulation | n tolerance |

|----------------|------|---------|------------|-------------|

| Output voltage | Max. | Min     | Max.       | Min.        |

| +5V            | 25.0 | 0       | +5%        | -5%         |

| +12V           | 33.0 | 2.0     | +5%        | -5%         |

| -12V           | 0.8  | 0.0     | +10%       | -10%        |

| +3.3V          | 25.0 | 0       | +5%        | -5%         |

| +5VSB          | 3    | 0.1     | +5%        | -5%         |

<sup>\*\*\* +5</sup>V and +3.3V total output max : 170W \*\*\*

When doing the cross regulation test(one output channel at high load and the other output channels at low load), it is requested to set the higher output channel at 80% max. of its spec., and the lower output channels at 20% max. of theirs.

#### 3.2 Regulation

| Output DC | Line                  |

|-----------|-----------------------|

| voltage   | regulation            |

| +5V       | ±50mV                 |

| +12V      | $\pm 120 \mathrm{mV}$ |

| -12V      | $\pm 120 \mathrm{mV}$ |

| +3.3V     | $\pm 50 \mathrm{mV}$  |

| +5VSB     | ±50mV                 |

<sup>\*\*\*</sup> Total output max : 420W \*\*\*

#### 3.3 Ripple and noise

#### 3.3.1 Specification

| +5V   | 50mV (P-P)  |

|-------|-------------|

| +12V  | 120mV (P-P) |

| -12V  | 120mV (P-P) |

| +3.3V | 50mV (P-P)  |

| +5VSB | 50mV (P-P)  |

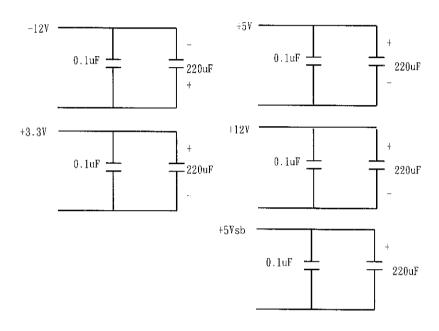

#### 3.3.2 Ripple voltage test circuit

0.1uf is ceramic, the other is electrolytic capacitor. Noise bandwidth is from DC to 20Mhz

#### 3.4 Overshoot

Any overshoot at turn on or turn off shall be less than 10% of the nominal voltage value, all output shall be within the regulation limit of section 3.1 before issuing the power good signal of section 6.0.

#### 3.5 Efficiency

Power supply efficiency >80% at 24V, full load.

#### 4.0 Protection

#### 4.1 Input (primary)

The input power line must have an over power protection device in accordance with safety requirement of section 8.0

#### 4.2 Output (secondary)

#### 4.2.1 Over power protection

The power supply shall provide over power protection on the power supply latches all DC output into a shutdown state. Over power of this type shall cause no damage to power supply , after over load is removed and a power on/off cycle is initiated, the power supply will restart.

Trip point total power min. 110%, max. 150%.

#### 4.2.2 Over voltage protection

If an over voltage fault occurs, the power supply will latch all DC output into a shutdown state before

+5V : 5.6V  $\sim$  6.5V +3.3V : 3.6V  $\sim$  4.3V +12V : 13.2V  $\sim$  15 V

#### 4.2.3 Short circuit

A: A short circuit placed on any DC output to DC return shall cause no damage.

B: The power supply shall be latched in case any short circuit is taken place at +5V, +3.3V, +12V, -12V output.

C: The power supply shall be auto-recovered in case any short circuit is taken place at +5VSB.

#### 4.2.4 Over current protection

If an over current fault occurs, the power supply will latch all DC output into a shutdown state.

|       | Min   | Typical | Max   |

|-------|-------|---------|-------|

| +3.3V | 27.5A | 32.5A   | 37.5A |

| +5V   | 27.5A | 32.5A   | 37.5A |

| +12V  | 36.3A | 42.9A   | 49.5A |

#### 5.0 Power supply sequencing

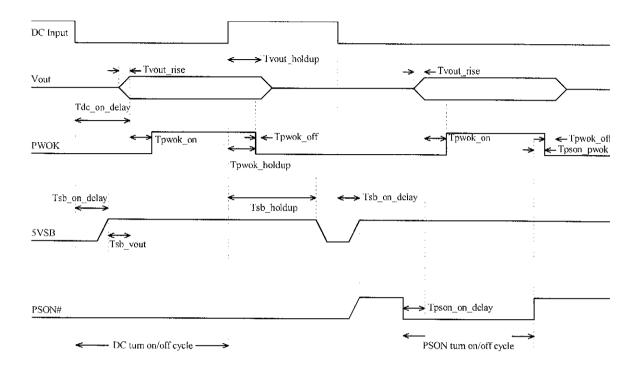

5.1 Power on (see fig.1)

#### 5.2 Hold up time

When power shutdown DC output 12V must be maintain 1.6 msec at 24V

5.3 Power off sequence (see fig. 1)

#### 6.0 Signal requirements

6.1 Power good signal (see fig. 1)

The power supply shall provide a "power good" signal to reset system logic, indicate proper operation of the power supply.

At power on , the power good signal shall have a turn on delay of at least 100ms but not greater than 500ms after the output voltages have reached their respective minimum sense levels.

#### 7.0 Environment

7.1 Temperature

Operating temperature

Non-Operating temperature

0 to 40 degrees centigrade -20 to 80 degrees centigrade

Operating temperature from 0°C should start from DC 24V

7.2 Humidity

Operating humidity

20% to 80%

Non-operating humidity

10% to 90%

7.3 Insulation resistance

Primary to secondary Primary to Frame Gnd

: 20 meg. ohm min. 500 VDC : 20 meg. ohm min. 500 VDC

7.4 Dielectric withstanding voltage

For approval purpose:

Primary to secondary

: 1.5K VAC for 1 sec.

Primary to Frame Gnd

: 1.5K VAC for 1 sec.

#### 8.0 Safety

8.1 Underwriters laboratory (UL).

The power supply designed to meet UL 60950.

8.2 TUV Standards

The power supply shall be designed to meet TUV EN-60950.

8.3 CB

The power supply shall be designed to meet CB IEC 60950.

#### 9.0 Reliability

9.1 Burn in

All products shipped to customer must be processed by burn-in. The burn- in shall be performed at full load.

#### 10.0 Mechanical requirements

Physical dimension : 225 mm \* 100 mm \* 40.5mm (D \*W\* H)

### 11.0 DC output cable drawing (see attached drawing)

| Item           | Description                                                                                            | MIN | MAX  | UNITS |

|----------------|--------------------------------------------------------------------------------------------------------|-----|------|-------|

| Tsb_on_delay   | Delay from DC being applied to 5VSB being within regulation.                                           |     | 2500 | ms    |

| Tdc_on_delay   | Delay from DC being applied to all output voltages being within regulation.                            |     | 4000 | ms    |

| Tvout_holdup   | Time all output voltages stay within regulation after loss of DC.                                      | 1.6 |      | ms    |

| Tpwok holdup   | Delay from loss of DC to deassertion of PWOK.                                                          | 0.6 |      | ms    |

| Tpson_on_delay | Delay from PSON# active to output voltages within regulation limits.                                   | 5   | 400  | ms    |

| Tpson_pwok     | Delay from PSON# deactive to PWOK being deasserted.                                                    |     | 50   | ms    |

| Tpwok_on       | Delay from output voltages within regulation limits to PWOK asserted at turn on.                       | 100 | 500  | ms    |

| Tpwok_off      | Delay from PWOK deasserted to output voltages (3.3V, 5V, 12V, -12V) dropping out of regulation limits. | 1   |      | ms    |

| Tsb_vout       | Delay from 5VSB being in regulation to O/Ps being in regulation at DC turn on.                         | 5   | 1000 | ms    |

| Tsb_holdup     | Time 5VSB output voltage stays within regulation after loss of DC.                                     | 2   |      | ms    |

| Tvout_rise     | Output voltage rise time from each main output.                                                        | 5   | 20   | ms    |

《Figure 1》